Empowering Tomorrow's Engineers: MLIR-Based Toolchain for Transforming Python Neural Networks into Verilog Hardware

-

:

HiWi

-

Starting date:

ab 11 / 2023

- Contact person:

Contact to supervisors only in english.

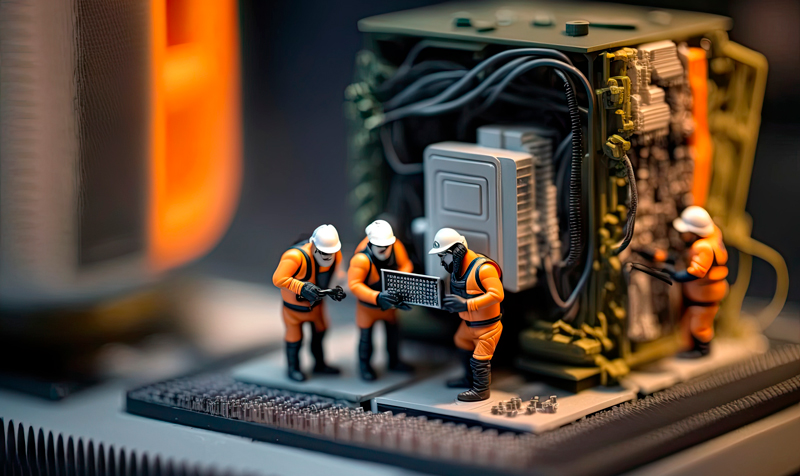

Empowering Tomorrow's Engineers: MLIR-Based Toolchain for Transforming Python Neural Networks into Verilog Hardware

Context

Neural Networks are an ideal target for realization on an FPGA. Their simple architecture, consisting only of dataflow elements, enabled the design of architectures with high throughput and low latency. However, modern networks introduce control flow elements that limit the usability of static scheduling employed my todays HLS tool. To overcome this, dynamic high-level synthesis allows the designer to employ localized scheduling decisions via classical handshake signals.

Tasks

Attention, aspiring engineers! Join us in a significant endeavor. This thesis explores the conversion of Python neural networks into Verilog hardware. Using MLIR and LLVM, we're delving into the depth of high-level synthesis, bringing algorithms to dynamic hardware.

This project isn't just another task; it's the honest, hands-on work that reshapes the landscape of hardware design. We're earnestly exploring the intricate blend of machine learning and synthesis. It's a chance to contribute to the future of technology, making a tangible impact.

Join us in this journey of knowledge and innovation. Together, let's pioneer a new chapter in hardware design.

Requirements

- Knowledge about C++

- Knowledge about hardware design is beneficial

- Interest in embedded design