Compiler-Based Integration of Neural Network Accelerators

- Subject:Hardware Accelerated Neural Networks

- Type:Masterarbeit

- Tutor:

Compiler-Based Integration of Neural Network Accelerators

Context

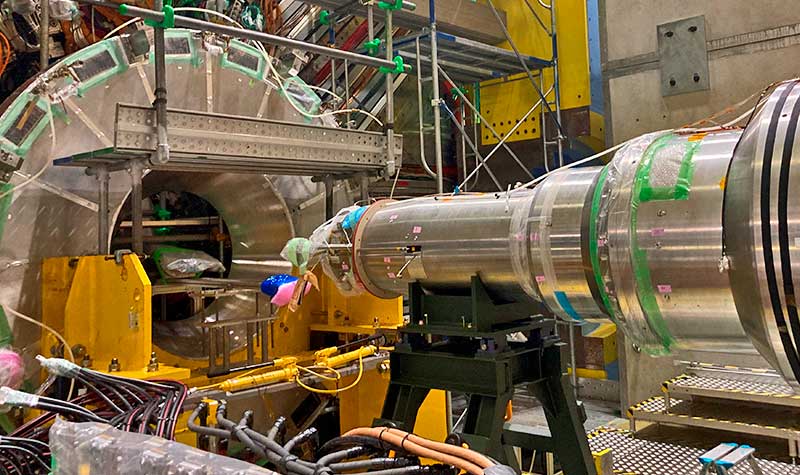

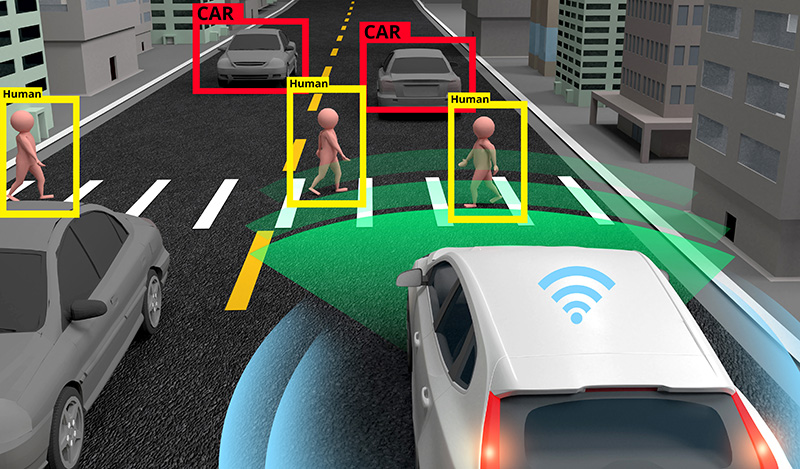

In recent years, the demand for implementations of neural networks in embedded systems has increased significantly. Especially in the areas of radar, experimental physics and in communication technology, real-time capable neural networks play an increasing role in signal processing. At ITIV, we are therefore conducting research in several projects on the automated hardware implementation of diverse network architectures.

Tasks

In recent years, frameworks for the automated implementation of neural networks on FPGAs have become established. However, toolchains such as hls4ml or FINN quickly reach their limits, especially when novel network architectures are to be investigated. The use of software compilers for hardware optimization promises new possibilities in the field of high-level synthesis. These allow optimizations of the entire network architecture as well as of the individual layers. The goal of this work is the implementation of an application-specific network architecture by means of high-level synthesis on a freely chosen use case.

Requirements

- Experience with C/C++

- First experiences with Verilog or High-Level-Synthesis

- Interest in the implementation of neural networks in embedded systems