Compiler-Based Integration of Neural Network Accelerators

- Forschungsthema:Hardware Accelerated Neural Networks

- Typ:Masterarbeit

- Betreuung:

Compiler-Based Integration of Neural Network Accelerators

Kontext

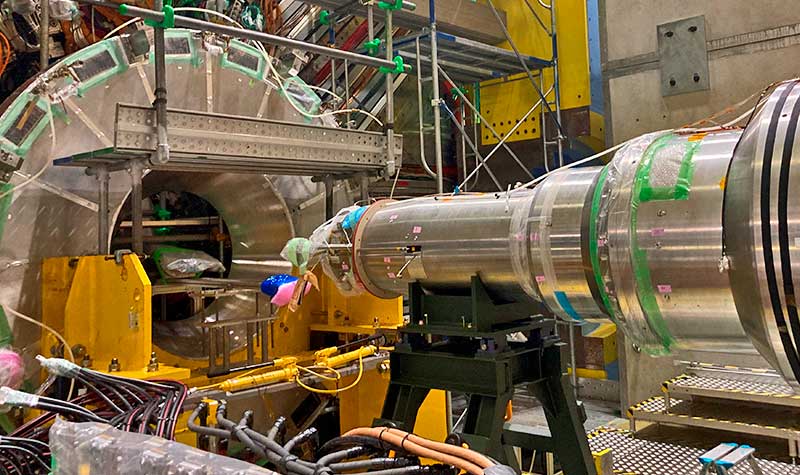

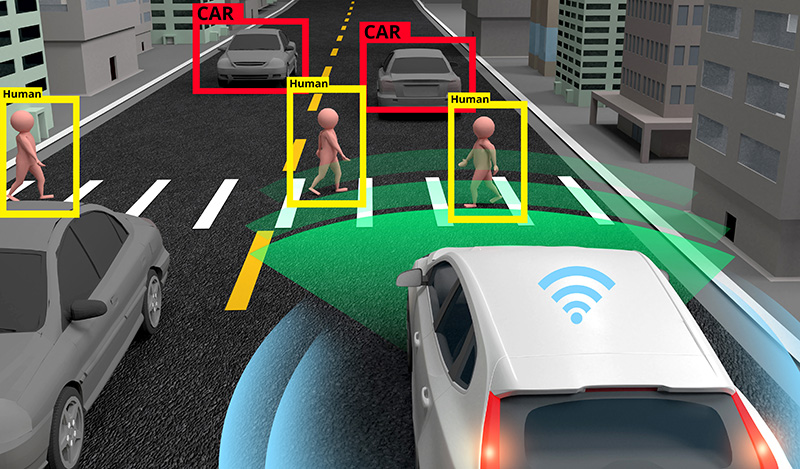

In den letzten Jahren ist die Nachfrage nach Implementierungen neuronaler Netze in eingebetteten Systemen stark angestiegen. Insbesondere in den Bereichen Radar, Experimentalphysik und in der Kommunikationstechnik spielen echtzeitfähige Neuronale Netze eine zunehmende Bedeutung in der Signalverarbeitung. Am ITIV forschen wir deshalb in mehreren Projekten an der automatisierten Hardwareumsetzung diverser Netzarchitekturen.

Aufgaben

In den letzten Jahren haben sich Frameworks zur automatisierten Umsetzung neuronaler Netze auf FPGAs etabliert. Toolchains wie hls4ml oder FINN stoßen dabei jedoch schnell an Ihre Grenzen, insbesondere wenn neuartige Netzarchitekturen untersucht werden sollen. Die Verwendung von Softwarecompilern zur Hardwareoptimierung versprechen neue Möglichkeiten im Fachbereich der High-Level-Synthese. Diese ermöglichen Optimierungen sowohl der gesamten Netzwerkarchitektur, als auch der einzelnen Layer. Ziel dieser Arbeit ist die Umsetzung einer applikationsspezifischen Netzarchitektur mittels High-Level-Synthese an einem frei gewählten Usecase.

Voraussetzungen

- Erfahrung im Umgang C/C++

- Erste Erfahrungen mit Verilog oder High-Level-Synthese

- Interesse an der Implementierung Neuronaler Netze in eingebetteten Systemen