Safe and Robust Machine Learning - Hardware Perspective

- Subject:Safe and Robust Machine Learning, Hardware Architectures, DNN Accelerators

- Type:Bachelor-/ Masterarbeit

- Tutor:

Safe and Robust Machine Learning - Hardware Perspective

Context

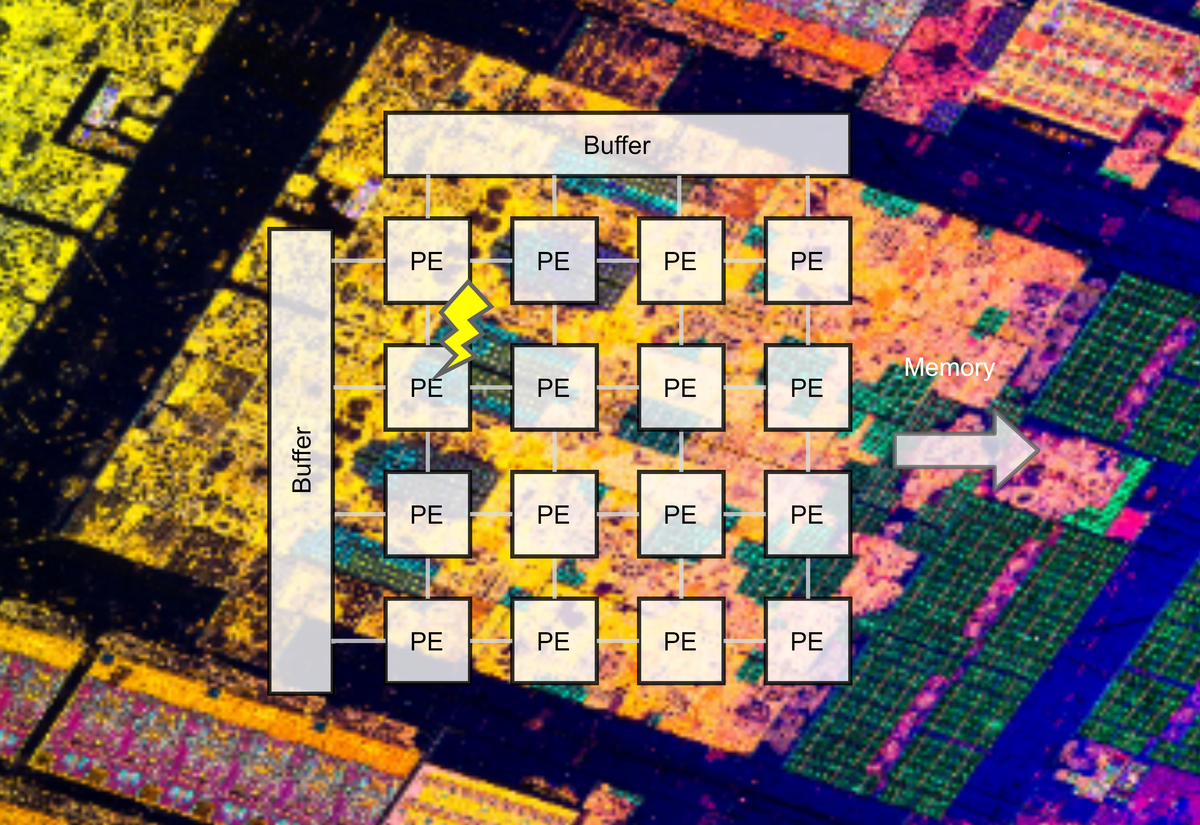

Machine learning is a promising approach for object recognition or segmentation in diverse domains. However, with the increasing use of machine learning models in safety-critical applications, it is also important to ensure safety/reliability as well as to increase the robustness of the ML models. From the hardware side, important aspects here include protection against transient random errors. From the software side, the estimation of the uncertainty of the neural networks is of particular interest.

The goal of this bachelor/master thesis is to improve the robustness and reliability on hardware level. For this purpose, own hardware accelerators can be designed, but also existing open-source hardware accelerators from research can be analyzed and extended. Especially RISC-V platforms like Chipyard play a central role.

Tasks

- Overview of the current literature and state of the art

- Design and implementation of concepts for safety mechanisms on hardware level, especially for DNN accelerators and SoCs

- Evaluation of the developed techniques based on benchmarks and use cases

- Discussion of the results and derivation of conclusions

Prerequisites

- Strong motivation for the topic of hardware design and machine learning and independent problem solving skills

- Knowledge in hardware design should be present, the concrete HDL plays a minor role (VHDL, Verilog, Chisel, ...)

- Basic knowledge in ML and neural networks is an advantage