Dr.-Ing. Dipl.-Inform. Tanja Harbaum

- Team leader of the working groups "Design of adaptive hardware architectures" and "AI in embedded systems"

- Group: Prof. Becker

- Room: 125.2

CS 30.10 - Phone: +49 721 608-47169

- harbaum ∂does-not-exist.kit edu

Engesserstr. 5

76131 Karlsruhe

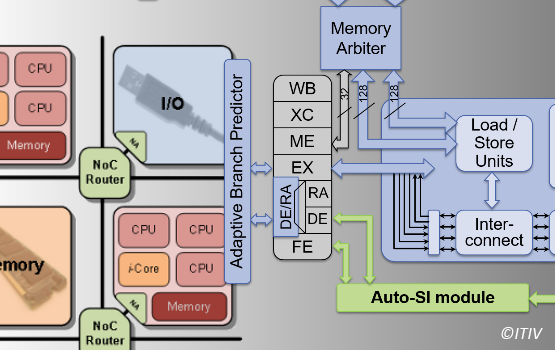

Design of adaptive hardware architectures

The demands laid down microarchitectures are increasing steadily, and much of the technological innovation of recent decades has only been made possible by the progress of the semiconductor industry and the accomplished increases in integrated circuit performance. A further increase of the

performance of integrated circuits is no longer self-evident, because physical limits will be reached soon. New architectures have to be designed in order to meet the increasing demands at this point.

Artificial intelligence in embedded systems

The performance of embedded systems can be increased enormously by integrating AI algorithms that are adapted to the embedded hardware. Through a hardware/software co-design, a fast and efficient AI execution on embedded systems can be realized. For the development of new cyber-physical systems (CPS) and Internet of Things (IoT) products, AI is becoming an increasingly important factor.

| title | type |

|---|---|

| AI-based Multi-Modal Sensor Fusion for Handwriting Trajectory Reconstruction | Master thesis |

| Methodology for evaluating model-accelerator co-design in deep learning | Masterarbeit |

Supervised student works (selection)

- MA: “Konzeptioneller Entwurf eines modularen Sensornetzwerks für intelligente Textilanwendungen”

- BA: ”Evaluation of Various Sensor Fusion Parameters for Online Handwriting Recognition and Trajectory Reconstruction”

- MA: “Evaluation of Robustness against changing weather conditions of Multi Modal AI-based Object Detection”

- MA: “Conceptual and Physical Design of a Hybrid Flexible Electronic System (HyFES) for Motion Tracking”

- SA: “Appropriate Adaptive Algorithms Facing Emerging Challenges for Wearables”

- SA: “A Review of Approximate Computing methods for a Universal Approximate Hardware Accelerator”

- BA: "Design and Modeling of a Runtime Adaptive Accelerator for a Reconfigurable Processor Architecture"

- MA: "Integration of runtime adaptive reconfiguration of hardware accelerators into a LEON3 architecture"

- BA: "Design, Implementation and Evaluation of a Pipeline Architecture for an FPGA Memory Architecture with Pattern Recognition Capability"

- MA: "Entwurf, Implementierung und Evaluierung einer FPGA-Speicherstruktur mit der Fähigkeit der Mustererkennung"

- BA: "Design, Implementation and Evaluation of a Memory Architecture in XILINX B-RAM"

Publications

Kreß, F.; Hoefer, J.; Lin, Q.; Schmidt, P.; Zhu, Z.; Zhu, Y.; Harbaum, T.; Wang, Y.; Becker, J.

2025. 2025 26th International Symposium on Quality Electronic Design (ISQED), 23rd-24th April 2025, San Francisco, 1–8, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/ISQED65160.2025.11014471

Hoefer, J.; Stammler, M.; Kreß, F.; Hotfilter, T.; Harbaum, T.; Becker, J.

2024. IEEE International Symposium on Defect and Fault Tolerance in VLSI and Technologisch Systems (DFT), Didcot, United Kingdom, 08-10 October 2024, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/DFT63277.2024.10753546

Schmidt, P.; Topko, I.; Stammler, M.; Harbaum, T.; Becker, J.; Berner, R.; Ahmed, O.; Jagielski, J.; Seidler, T.; Abel, M.; Kreutzer, M.; Kirschner, M.; Betancourt, V. P.; Sehm, R.; Groth, L.; Neskovic, A.; Meyer, R.; Mulhem, S.; Berekovic, M.; Probst, M.; et al.

2024. 27th Design, Automation and Test in Europe Conference and Exhibition (DATE 2024), 6 S., Institute of Electrical and Electronics Engineers (IEEE). doi:10.23919/DATE58400.2024.10546796

Topko, I.; Harbaum, T.; Becker, J.

2024. 2024 IEEE Nordic Circuits and Systems Conference (NorCAS). Ed.: J. Nurmi, 7 S., Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/NorCAS64408.2024.10752456

Serdyuk, A.; Kreß, F.; Topko, I.; Harbaum, T.; Becker, J.; Hamann, T.; Kämpf, P.

2024. 2024 Sensor Data Fusion: Trends, Solutions, Applications (SDF), Bonn, Germany, 25-27 November 2024, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SDF63218.2024.10773805

Schmidt, P.; Pfau, J.; Hotfilter, T.; Stammler, M.; Harbaum, T.; Becker, J.

2024. 2024 IEEE 37th International System-on-Chip Conference (SOCC), Dresden, 16th-19th September 2024, 1–6, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC62300.2024.10737723

Krausse, J.; Neher, M.; Fuerst-Walter, I.; Weigelt, C.; Harbaum, T.; Knobloch, K.; Becker, J.

2024. 2024 IEEE 37th International System-on-Chip Conference (SOCC), Dresden, 16th-19th September 2024, 1–6, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC62300.2024.10737770

Stammler, J. M.; Hoefer, J.; Schmidt, P.; Harbaum, T.; Becker, J.

2024. 2024 IEEE Computer Society Annual Symposium on VLSI (ISVLSI), 656 – 660, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/ISVLSI61997.2024.00125

Neu, M.; Karle, C.; Schmidt, P.; Höfer, J.; Harbaum, T.; Becker, J.

2024. IEEE 37th International System-on-Chip Conference (SOCC 2024), 6 S., Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC62300.2024.10737798

Karle, C.; Neu, M.; Nuss, B.; Witte, L.; Scheder, A.; Waldner, E.; Shkurtaj, E.; Harbaum, T.; Becker, J.

2024. IEEE 37th International System-on-Chip Conference (SOCC 2024), 6 S., Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC62300.2024.10737777

Karle, C.; Neu, M.; Nuss, B.; Chen, J.; Witte, L.; Scheder, A.; Harbaum, T.; Becker, J.

2024. IEEE 37th International System-on-Chip Conference (SOCC 2024), 6 S., Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC62300.2024.10737765

Kreß, F.; Serdyuk, A.; Kobsar, D.; Hotfilter, T.; Höfer, J.; Harbaum, T.; Becker, J.

2024. 2024 IEEE 37th International System-on-Chip Conference (SOCC), Dresden, Germany, 16-19 September 2024, 126–131, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC62300.2024.10737863

Kreß, F.; El Annabi, E. M.; Hotfilter, T.; Hoefer, J.; Harbaum, T.; Becker, J.

2024. 2024 IEEE Computer Society Annual Symposium on VLSI (ISVLSI), 1st-3rd July 2024, Knoxville, 39–44, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/ISVLSI61997.2024.00019

Kreß, F.; Sidorenko, V.; Topko, I.; Unger, K.; Harbaum, T.; Becker, J.

2024. 2024 IEEE 3rd German Education Conference (GECon), Munich, Germany, 05-07 August 2024, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/GECon62014.2024.10734007

Harbaum, T.; Serdyuk, A.; Kreß, F.; Hamann, T.; Barth, J.; Kämpf, P.; Imbert, F.; Soullard, Y.; Tavenard, R.; Anquetil, E.; Delahaie, J.

2024. Proceedings - 2024 Design, Automation and Test in Europe Conference and Exhibition (DATE), 6 S., Institute of Electrical and Electronics Engineers (IEEE). doi:10.23919/DATE58400.2024.10546623

Lesniak, F.; Gutermann, A.; Harbaum, T.; Becker, J.

2024. GLSVLSI ’24: Proceedings of the Great Lakes Symposium on VLSI 2024, 151 – 157, Association for Computing Machinery (ACM). doi:10.1145/3649476.3658737

Hoefer, J.; Gauß, M.; Adams, M.; Kreß, F.; Kempf, F.; Karle, C.; Harbaum, T.; Barth, A.; Becker, J.

2024. 2024 IEEE International Symposium on Circuits and Systems (ISCAS), Singapore, Singapore, 19-22 May 2024, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/ISCAS58744.2024.10557955

Serdyuk, A.; Kreβ F.; Hiegle, M.; Harbaum, T.; Becker, J.; Imbert, F.; Soullard, Y.; Tavenard, R.; Anquetil, E.; Barth, J.; Kämpf, P.

2024. 2023 IEEE 9th World Forum on Internet of Things (WF-IoT), Aveiro, 12th - 27th October 2023, 01–06, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/WF-IoT58464.2023.10539488

Harbaum, T.; Topko, I.; Serdyuk, A.; Fürst-Walter, I.; Kreß, F.; Becker, J.

2024. 3rd Workshop on Deep Learning for IoT (DL4IoT-2024)

Stammler, M.; Hamann, M.; Harbaum, T.; Becker, J.

2024. 2023 26th Euromicro Conference on Digital System Design (DSD), Golem, 6th - 8th September 2023, 561 – 568, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/DSD60849.2023.00083

Lesniak, F.; Harbaum, T.; Becker, J.

2024. 2023 IEEE 16th International Symposium on Embedded Multicore/Many-core Systems-on-Chip (MCSoC), Singapur, 18th - 21st December 2023, 340–346, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/MCSoC60832.2023.00057

Stammler, M.; Höfer, J.; Kraus, D.; Schmidt, P.; Hotfilter, T.; Harbaum, T.; Becker, J.

2023. Procedia Computer Science, 222, 499 – 508. doi:10.1016/j.procs.2023.08.188

Kreß, F.; Sidorenko, V.; Schmidt, P.; Hoefer, J.; Hotfilter, T.; Walter, I.; Harbaum, T.; Becker, J.

2023. Computer Networks, 229, Article no: 109759. doi:10.1016/j.comnet.2023.109759

Kempf, F.; Hoefer, J.; Harbaum, T.; Becker, J.; Fasfous, N.; Frickenstein, A.; Voegel, H.-J.; Friedrich, S.; Wittig, R.; Matúš, E.; Fettweis, G.; Lueders, M.; Blume, H.; Benndorf, J.; Grantz, D.; Zeller, M.; Engelke, D.; Eickel, K.-H.

2023. 2023 Design, Automation & Test in Europe Conference & Exhibition (DATE), Antwerp, Belgium, 17-19 April 2023, Institute of Electrical and Electronics Engineers (IEEE). doi:10.23919/DATE56975.2023.10137257

Kreß, F.; Serdyuk, A.; Hiegle, M.; Waldmann, D.; Hotfilter, T.; Hoefer, J.; Hamann, T.; Barth, J.; Kämpf, P.; Harbaum, T.; Becker, J.

2023. 26th Euromicro Conference on Digital System Design (DSD 2023), 569–576, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/DSD60849.2023.00084

Anantharajaiah, N.; Lesniak, F.; Harbaum, T.; Becker, J.

2023. 2023 IEEE 16th International Symposium on Embedded Multicore/Many-core Systems-on-Chip (MCSoC), 38 – 44, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/MCSoC60832.2023.00014

Fürst-Walter, I.; Nappi, A.; Harbaum, T.; Becker, J.

2023. 2023 IEEE/RSJ International Conference on Intelligent Robots and Systems (IROS), Detroit, Mi, 1st-5th October 2023, 10888 – 10893, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/IROS55552.2023.10341256

Hotfilter, T.; Hoefer, J.; Merz, P.; Kreß, F.; Kempf, F.; Harbaum, T.; Becker, J.

2023. 2023 IEEE 36th International System-on-Chip Conference (SOCC), Santa Clara, USA, 05-08 September 2023, 1–6, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC58585.2023.10256738

Lesniak, F.; Harbaum, T.; Becker, J.

2023. 2023 IEEE 36th International System-on-Chip Conference (SOCC), Santa Clara, USA, 05-08 September 2023, 1–6, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC58585.2023.10257090

Kreß, F.; Pfau, J.; Kempf, F.; Schmidt, P.; He, Z.; Harbaum, T.; Becker, J.

2023. 2023 IEEE Nordic Circuits and Systems Conference (NorCAS), 31st October - 1st November 2023, Aalborg, Denmark, 1–7, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/NorCAS58970.2023.10305469

Anantharajaiah, N.; Xu, Y.; Lesniak, F.; Harbaum, T.; Becker, J.

2023. IEEE Computer Society Annual Symposium on VLSI (ISVLSI), 1–6, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/ISVLSI59464.2023.10238569

Hoefer, J.; Hotfilter, T.; Kreß, F.; Qiu, C.; Harbaum, T.; Becker, J.

2023. Computer Vision Systems – 14th International Conference, ICVS 2023, Vienna, Austria, September 27–29, 2023. Ed.: H. Christensen, 299–309, Springer Nature Switzerland. doi:10.1007/978-3-031-44137-0_25

Hotfilter, T.; Höfer, J.; Kreß, F.; Kempf, F.; Kraft, L.; Harbaum, T.; Becker, J.

2023. 2023 IEEE 5th International Conference on Artificial Intelligence Circuits and Systems (AICAS), 1–5, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/AICAS57966.2023.10168566

Hoefer, J.; Kempf, F.; Hotfilter, T.; Kreß, F.; Harbaum, T.; Becker, J.

2023. Proceedings of the Great Lakes Symposium on VLSI 2023, 287–292, Association for Computing Machinery (ACM). doi:10.1145/3583781.3590226

Lesniak, F.; Anantharajaiah, N.; Harbaum, T.; Becker, J.

2023. RAPIDO ’23: Proceedings of the DroneSE and RAPIDO: System Engineering for constrained embedded systems, 31–38, Association for Computing Machinery (ACM). doi:10.1145/3579170.3579262

Hotfilter, T.; Schmidt, P.; Höfer, J.; Kreß, F.; Harbaum, T.; Becker, J.

2023. DroneSE and RAPIDO: System Engineering for constrained embedded systems, 73–78, Association for Computing Machinery (ACM). doi:10.1145/3579170.3579258

Kreß, F.; Hoefer, J.; Hotfilter, T.; Walter, I.; El Annabi, E. M.; Harbaum, T.; Becker, J.

2023. Machine Learning and Principles and Practice of Knowledge Discovery in Databases. Hrsg.: I. Koprinska. Pt. 1, 557–568, Springer International Publishing. doi:10.1007/978-3-031-23618-1_37

Kempf, F.; Höfer, J.; Kreß, F.; Hotfilter, T.; Harbaum, T.; Becker, J.

2022. Conference Proceedings: 2022 IEEE 35th International System-on-Chip Conference (SOCC) Ed.: S. Sezer, 1–6, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC56010.2022.9908110

Kreß, F.; Hoefer, J.; Hotfilter, T.; Walter, I.; Sidorenko, V.; Harbaum, T.; Becker, J.

2022. 18th International Conference on Distributed Computing in Sensor Systems (DCOSS), 133–140, IEEEXplore. doi:10.1109/DCOSS54816.2022.00034

Kreß, F.; Serdyuk, A.; Hotfilter, T.; Höfer, J.; Harbaum, T.; Becker, J.; Hamann, T.

2022. 2022 11th Mediterranean Conference on Embedded Computing (MECO). Ed.: IEEE, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/MECO55406.2022.9797131

Pfau, J.; Reuter, M.; Harbaum, T.; Hofmann, K.; Becker, J.

2020. 2019 32nd IEEE International System-on-Chip Conference (SOCC), Singapore, 3-6 Sept. 2019, 294–299, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC46988.2019.1570548289

Harbaum, T.

2019. Karlsruher Institut für Technologie (KIT). doi:10.5445/IR/1000096122

Harbaum, T.; Balzer, M.; Becker, J.; Weber, M.

2018. Proceedings of the 31th IEEE International System-on-Chip Conference (SOCC), 118–123, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC.2018.8618493

Harbaum, T.; Schade, C.; Damschen, M.; Tradowsky, C.; Bauer, L.; Henkel, J.; Becker, J.

2017. 2017 30th IEEE International System-on-Chip Conference (SOCC), Munich, 5–8 September 2017, 153–158, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC.2017.8226027

CMS Collaboration; Khachatryan, V.; Sirunyan, A. M.; Tumasyan, A.; Adam, W.; Asilar, E.; Bergauer, T.; Brandstetter, J.; Brondolin, E.; Dragicevic, M.; Erö, J.; Flechl, M.; Friedl, M.; Frühwirth, R.; Ghete, V. M.; Hartl, C.; Hörmann, N.; Hrubec, J.; Jeitler, M.; Harbaum, T.; et al.

2016. Physical review / D, 93 (11), 112009. doi:10.1103/PhysRevD.93.112009

Tradowsky, C.; Harbaum, T.; Masing, L.; Becker, J.

2016. Best of ISVLSI 2016, Pittsburgh, Pennsylvania, U.S.A., July 11-13, 2016, Springer

Harbaum, T.; Seboui, M.; Balzer, M.; Becker, J.; Weber, M.

2016. 24th IEEE International Symposium on Field-Programmable Custom Computing Machines, FCCM 2016; Washington; United States; 1 May 2016 through 3 May 2016, 184–191, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/FCCM.2016.52

Amstutz, C.; Ball, F. A.; Balzer, M. N.; Brooke, J.; Calligaris, L.; Cieri, D.; Clement, E. J.; Hall, G.; Harbaum, T. R.; Harder, K.; Hobson, P. R.; Iles, G. M.; James, T.; Manolopoulos, K.; Matsushita, T.; Morton, A. D.; Newbold, D.; Paramesvaran, S.; Pesaresi, M.; Reid, I. D.; et al.

2016. 20th Real Time Conference (RT), IEEE-NPSS, Padova, Italy, 6-10 June 2016, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/RTC.2016.7543102

Amstutz, C.; Ball, F. A.; Balzer, M. N.; Brooke, J.; Calligaris, L.; Cieri, D.; Clement, E. J.; Hall, G.; Harbaum, T. R.; Harder, K.; Hobson, P. R.; Iles, G. M.; James, T.; Manolopoulos, K.; Matsushita, T.; Morton, A. D.; Newbold, D.; Paramesvaran, S.; Pesaresi, M.; Reid, I. D.; et al.

2016. 20th Real Time Conference (RT) IEEE-NPSS, Padova, Italy, 6-10 June 2016, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/RTC.2016.7543110

Aad, G.; Abbott, B.; Abdallah, J.; Abdinov, O.; Aben, R.; Abolins, M.; Abouzeid, O. S.; Abramowicz, H.; Abreu, H.; Abreu, R.; Abulaiti, Y.; Acharya, B. S.; Adamczyk, L.; Adams, D. L.; Adelman, J.; Adomeit, S.; Adye, T.; Affolder, A. A.; Agatonovic-Jovin, T.; Harbaum, T.; et al.

2015. Physical review letters, 114 (19), 191803. doi:10.1103/PhysRevLett.114.191803

Tradowsky, C.; Harbaum, T.; Deyerle, S.; Becker, J.

2013. IEEE Computer Society Annual Symposium on VLSI (ISVLSI’13), Natal, Brazil, August 5-7, 2013, 34–39, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/ISVLSI.2013.6654619

Oberländer, J.; Harbaum, T.; Kurz, G.; Ahmed, N.; Kos-Grabar, T.; Hermann, A.; Roenau, A.; Dillmann, R.

2012. Field robotics : proceedings of the 14th International Conference on Climbing and Walking Robots and the Support Technologies for Mobile Machines, CLAWAR 2011, Paris, France, 6-8 September 2011. Ed.: P. Bidaud, 233–240, World Scientific Publishing