Fabian Lesniak, Master of Desaster

- Wissenschaftlicher Mitarbeiter

- Group: Prof. Becker

- Room: 226.1

CS 30.10 - Phone: +49 721 608-42504

- fabian lesniak ∂does-not-exist.kit edu

Engesserstr. 5

76131 Karlsruhe

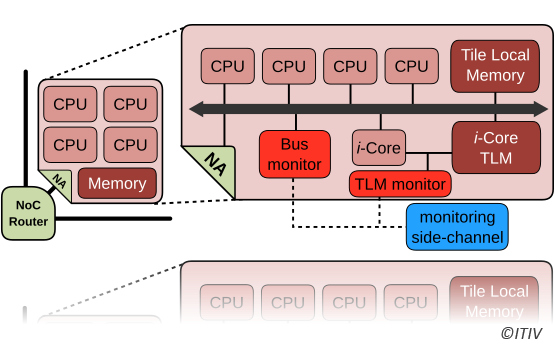

Design of heterogeneous manycore platforms

While performance requirements for integrated circuits continue to increase, the semiconductor industry is struggling to keep up. Problems with power density and static leakage came to the fore, while earlier effects such as Dennard scaling faded out. Instead, to gain further performance, the number of processor cores is increased. Such manycore systems with hundreds of processors require a different hardware design than classical embedded systems. The programmability of such systems also differs greatly, since problems have to be parallelized to a high degree.

Runtime adaptive hardware architectures

A modern system-on-chip must save chip area and power to allow the design of small, mobile devices with long battery life. Yet users expect very high computing power for very specific problems, such as media processing or neural network inference. By developing hardware architectures that are reconfigurable during runtime, they become more versatile and even future-proof for use cases that are not yet known at the time of development - with smaller chip area and fewer dark silicon effects. When developing such adaptive hardware architectures, various design parameters must be carefully weighed to ensure that the system is suitable for as many purposes as possible.

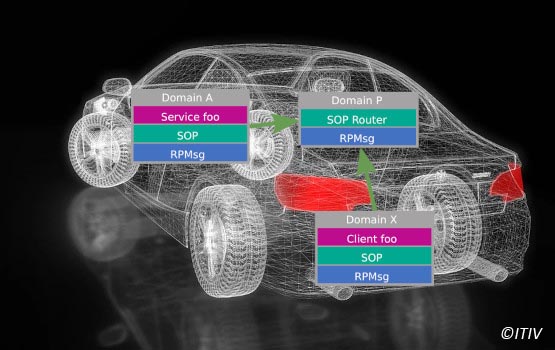

Hypervisor-based systems for safety-critical applications

Safety-critical applications are found in particular in the area of control and regulation of vehicles and systems. Such systems are complex to develop and maintain, since flawless functionality must be guaranteed - even after an update. By using modern virtualization technologies, the isolation of individual system components can be improved. This increases the complexity of the overall system and makes it more difficult to assess security. The aim of the research is to reduce the impediments of using a hypervisor in these areas.

| title | type |

|---|---|

| Developing a mapping tool for adaptive AI accelerators | Master thesis |

| Development of an AI accelerator model for design space exploration | Bachelor thesis |

| Titel |

|---|

| Aufbau und Weiterentwicklung eines Demonstrators für Over The Air Updates auf hochautomatisierten Fahrzeugen |

Supervised student works (selection)

- MA: "Verteiltes Echtzeit-Monitoring von Manycores"

- MA: "Design eines prozessorbasierten Near-Memory-Beschleunigers"

- MA: "Entwicklung eines dynamischen und flexiblen Speichercontrollers für Manycore-Prototypen"

- MA: "Channel Estimation of Dynamic Intra-Tile Reallocatable Cache in Homogeneous GPPs"

- MA: "Hypervisor-Gastüberwachung in Safety-Critical Systems"

- MA: "Implementing an AI Accelerator as a Special Instruction"

- BA: "ARM-Debugger für den Xen-Hypervisor"

- BA: "Implementierung eines approximativen Beschleunigers"

- BA: "Dynamische CNN-Beschleunigung für den i-Core Prozessor"

Publications

Lesniak, F.; Gutermann, A.; Harbaum, T.; Becker, J.

2024. GLSVLSI ’24: Proceedings of the Great Lakes Symposium on VLSI 2024, 151 – 157, Association for Computing Machinery (ACM). doi:10.1145/3649476.3658737

Lesniak, F.; Harbaum, T.; Becker, J.

2024. 2023 IEEE 16th International Symposium on Embedded Multicore/Many-core Systems-on-Chip (MCSoC), Singapur, 18th - 21st December 2023, 340–346, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/MCSoC60832.2023.00057

Anantharajaiah, N.; Lesniak, F.; Harbaum, T.; Becker, J.

2023. 2023 IEEE 16th International Symposium on Embedded Multicore/Many-core Systems-on-Chip (MCSoC), 38 – 44, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/MCSoC60832.2023.00014

Lesniak, F.; Harbaum, T.; Becker, J.

2023. 2023 IEEE 36th International System-on-Chip Conference (SOCC), Santa Clara, USA, 05-08 September 2023, 1–6, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC58585.2023.10257090

Anantharajaiah, N.; Xu, Y.; Lesniak, F.; Harbaum, T.; Becker, J.

2023. IEEE Computer Society Annual Symposium on VLSI (ISVLSI), 1–6, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/ISVLSI59464.2023.10238569

Lesniak, F.; Anantharajaiah, N.; Harbaum, T.; Becker, J.

2023. RAPIDO ’23: Proceedings of the DroneSE and RAPIDO: System Engineering for constrained embedded systems, 31–38, Association for Computing Machinery (ACM). doi:10.1145/3579170.3579262

Guissouma, H.; Hohl, C. P.; Lesniak, F.; Schindewolf, M.; Becker, J.; Sax, E.

2022. IEEE Access, 10, 57696–57717. doi:10.1109/ACCESS.2022.3176879

Masing, L.; Lesniak, F.; Becker, J.

2021. IEEE embedded systems letters, 13 (1). doi:10.1109/LES.2020.2995084

Lesniak, F.; Kreß, F.; Becker, J.

2021. Applied Reconfigurable Computing. Ed.: S. Derrien, 221–231, Springer Nature Switzerland. doi:10.1007/978-3-030-79025-7_15

Anantharajaiah, N.; Kempf, F.; Masing, L.; Lesniak, F. M.; Becker, J.

2019. Proceedings of the 12th International Workshop on Network on Chip Architectures (NoCArc 2019), Columbus, OH, Ocober 12-13, 2019, 1–6, Association for Computing Machinery (ACM). doi:10.1145/3356045.3360718

Masing, L.; Lesniak, F.; Becker, J.

2019. 15th International Symposium on Applied Reconfigurable Computing, ARC 2019; Darmstadt; Germany; 9 April 2019 through 11 April 2019, 319–333. doi:10.1007/978-3-030-17227-5_23

Werner, S.; Masing, L.; Lesniak, F.; Becker, J.

2015. 2015 25th International Conference on Field Programmable Logic and Applications (FPL), London, United Kingdom, 2–4 September 2015, Art.Nr. 7294020, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/FPL.2015.7294020