PARFAIT II

- Contact:

- Project group:

Prof. Becker

- Funding:

DFG

- Partner:

KIT, NaMLab, TU Darmstadt

- Startdate:

01.02.2022

- Enddate:

31.01.2025

PARFAIT II - Poweraware AmbipolaR Fpga ArchITecture II

Project goals

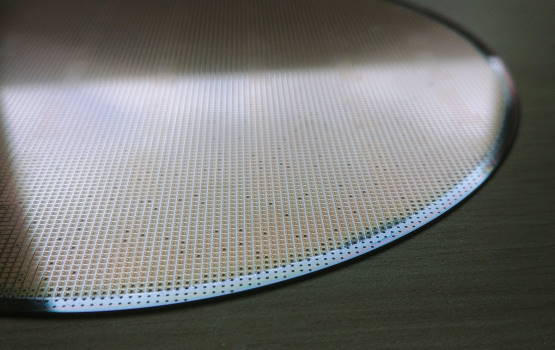

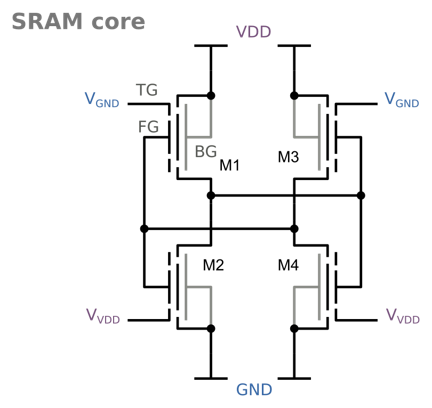

In PARFAIT II, planar reconfigurable field-effect transistors (RFETs) with electrically adjustable p- and n-conductivity are being researched. The focus of PARFAIT II is on the fabrication of the transistors, the development of logic gates and their use in complex circuits. For this, a reliable and reproducible fabrication process for planar RFETs has to be designed. Following a joint specification phase, the simulative models from PARFAIT I will be verified and adapted to real manufacturing conditions by designing, manufacturing and measuring test circuits. The foundations will be laid to be able to use reconfigurable transistors in real applications with scaled geometries on a larger scale. Further, PARFAIT II will investigate circuit- and system-level applications for which the simulated and measured characteristics of the RFETs explored are most promising. A major part of the project is the investigation of the temperature behavior of the RFET from the technology to the system level.

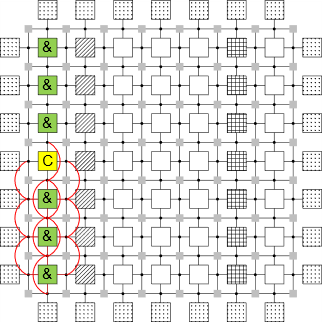

ITIV participation

ITIV will investigate dynamic compensation of PVT and aging effects on circuit and system level, especially for an FPGA architecture based on RFETs: According to measurements of propagation delays, the capability of the planar RFETs is used to adapt threshold voltages, leakage currents and switching currents of cells in a fine-granular way via the additional back gate, independent of the configured logic function (set via the front gates).