Central contents of his dissertation

Fabian's research has focused on adaptive computer architectures. He has developed a concept that enables computers for high-performance applications, such as those used in autonomous driving, to be both efficient (i.e. with low power loss) and flexible (for different types of algorithms). Flexibility is important in the automotive environment so that vehicles can be subsequently updated and the algorithms improved, e.g. for enhanced driving functions. At the same time, efficiency is also extremely important so that the range is not impaired too much and no unnecessary additional emissions are produced. The architectures he investigated were made more flexible through the targeted placement of embedded FPGA units, without compromising efficiency.

🎉 After the defense, Fabian's team members traditionally surprised him with a specially designed doctoral hat - handmade after work and full of loving details from his field of research. ITIV has been cultivating this tradition for many years, creating special moments every time.

The entire institute would like to congratulate Fabian on this great success!

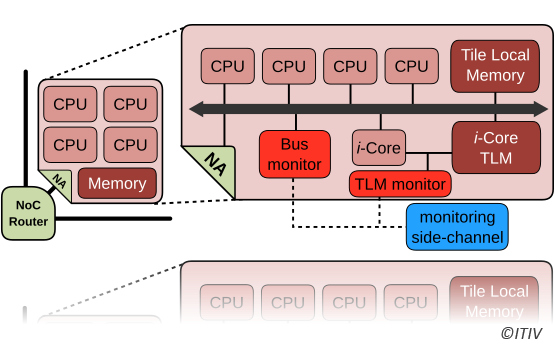

Design of heterogeneous manycore platforms

As performance requirements for integrated circuits continue to increase, the semiconductor industry is struggling to keep pace. Problems with power density and static leakage have come to the fore, while earlier effects such as denard scaling have been eliminated. To gain further performance, the number of processor cores is being increased instead. Such manycore systems with hundreds of processors require a different hardware design than classic embedded systems. The programmability of such systems is also very different, as problems have to be parallelized to a high degree.

Runtime-adaptive architectures

A modern system on chip must save chip area and power to enable the design of small, mobile devices with long battery life. Nevertheless, users expect very high computing power for very specific problems, such as media processing or neural network inference. By developing hardware architectures that are reconfigurable at runtime, they become more versatile and even future-proof for use cases that are not yet known at the time of development - with a smaller chip area and fewer dark silicon effects. When developing such adaptive hardware architectures, various design parameters must be carefully weighed up so that the system is suitable for as many purposes as possible.

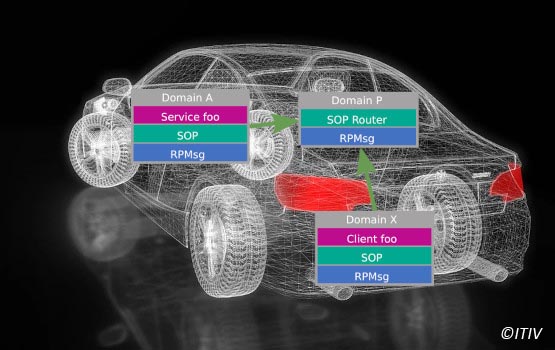

Hypervisor-based systems for safety-critical applications

Safety-critical applications are found in particular in the area of control and regulation of vehicles and systems. Such systems are complex to develop and maintain, as flawless functionality must be guaranteed - even after an update. By using modern virtualization technologies, the isolation of individual system components can be improved. This increases the complexity of the overall system and makes it more time-consuming to assess security. The aim of the research is to reduce the hurdles for the use of a hypervisor in these areas.

Supervised student projects (selection)

- MA: "Distributed real-time monitoring of manycores"

- MA: "Design of a processor-based near-memory accelerator"

- MA: "Development of a dynamic and flexible memory controller for manycore prototypes"

- MA: "Channel Estimation of Dynamic Intra-Tile Reallocatable Cache in Homogeneous GPPs"

- MA: "Hypervisor Guest Monitoring in Safety-Critical Systems"

- MA: "Implementing an AI Accelerator as a Special Instruction"

- BA: "ARM debugger for the Xen hypervisor"

- BA: "Implementation of an approximate accelerator"

- BA: "Dynamic CNN acceleration for the i-Core processor"

Publications

Gutermann, A.; Serdyuk, A.; Paraskevas, F.; Kiesa, H. T.; Lesniak, F.; Schwarz, J.; Hartmann, M.; Harbaum, T.; Becker, J.

2025. 2025 IEEE Nordic Circuits and Systems Conference, NorCAS 2025, Riga, 28th-29th October 2025, 1–7, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/NorCAS66540.2025.11231285

Stammler, M.; Lesniak, F.; Kumar, N. S.; Easwaran, A.; Becker, J.

2025. 2025 IEEE 38th International System-on-Chip Conference (SOCC), Dubai, 29th September 2025 - 1st October 2025, 1–6, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC66126.2025.11235395

Hoefer, J.; Lesniak, F. M.; Gutermann, A.; Wöran, F.; Harbaum, T.; Becker, J. E.

2025. 2025 IEEE 38th International System-on-Chip Conference (SOCC), Dubai, 29th September 2025 - 1st October 2025, 1–6, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC66126.2025.11235419

Karle, C.; Fuerst-Walter, I.; Schade, F.; Hoefer, J.; Lesniak, F.; Harbaum, T.; Becker, J.

2025. 2025 IEEE 4th German Education Conference (GECon), Hamburg, 21st-23rd July 2025, 1–5, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/GECon64629.2025.11369364

Lesniak, F.; Gutermann, A.; Harbaum, T.; Becker, J.

2024. GLSVLSI ’24: Proceedings of the Great Lakes Symposium on VLSI 2024, 151 – 157, Association for Computing Machinery (ACM). doi:10.1145/3649476.3658737

Lesniak, F.; Harbaum, T.; Becker, J.

2024. 2023 IEEE 16th International Symposium on Embedded Multicore/Many-core Systems-on-Chip (MCSoC), Singapur, 18th - 21st December 2023, 340–346, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/MCSoC60832.2023.00057

Anantharajaiah, N.; Lesniak, F.; Harbaum, T.; Becker, J.

2023. 2023 IEEE 16th International Symposium on Embedded Multicore/Many-core Systems-on-Chip (MCSoC), 38 – 44, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/MCSoC60832.2023.00014

Lesniak, F.; Harbaum, T.; Becker, J.

2023. 2023 IEEE 36th International System-on-Chip Conference (SOCC), Santa Clara, USA, 05-08 September 2023, 1–6, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC58585.2023.10257090

Anantharajaiah, N.; Xu, Y.; Lesniak, F.; Harbaum, T.; Becker, J.

2023. IEEE Computer Society Annual Symposium on VLSI (ISVLSI), 1–6, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/ISVLSI59464.2023.10238569

Lesniak, F.; Anantharajaiah, N.; Harbaum, T.; Becker, J.

2023. RAPIDO ’23: Proceedings of the DroneSE and RAPIDO: System Engineering for constrained embedded systems, 31–38, Association for Computing Machinery (ACM). doi:10.1145/3579170.3579262

Guissouma, H.; Hohl, C. P.; Lesniak, F.; Schindewolf, M.; Becker, J.; Sax, E.

2022. IEEE Access, 10, 57696–57717. doi:10.1109/ACCESS.2022.3176879

Masing, L.; Lesniak, F.; Becker, J.

2021. IEEE embedded systems letters, 13 (1). doi:10.1109/LES.2020.2995084

Lesniak, F.; Kreß, F.; Becker, J.

2021. Applied Reconfigurable Computing. Ed.: S. Derrien, 221–231, Springer Nature Switzerland. doi:10.1007/978-3-030-79025-7_15

Anantharajaiah, N.; Kempf, F.; Masing, L.; Lesniak, F. M.; Becker, J.

2019. Proceedings of the 12th International Workshop on Network on Chip Architectures (NoCArc 2019), Columbus, OH, Ocober 12-13, 2019, 1–6, Association for Computing Machinery (ACM). doi:10.1145/3356045.3360718

Masing, L.; Lesniak, F.; Becker, J.

2019. 15th International Symposium on Applied Reconfigurable Computing, ARC 2019; Darmstadt; Germany; 9 April 2019 through 11 April 2019, 319–333. doi:10.1007/978-3-030-17227-5_23

Werner, S.; Masing, L.; Lesniak, F.; Becker, J.

2015. 2015 25th International Conference on Field Programmable Logic and Applications (FPL), London, United Kingdom, 2–4 September 2015, Art.Nr. 7294020, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/FPL.2015.7294020