Entwicklung eines Mapping-Tools für adaptive KI-Beschleuniger

- Forschungsthema:KI-Beschleuniger

- Typ:Masterarbeit

- Datum:ab 06 / 2023

- Betreuung:

Entwicklung eines Mapping-Tools für adaptive KI-Beschleuniger

Kontext

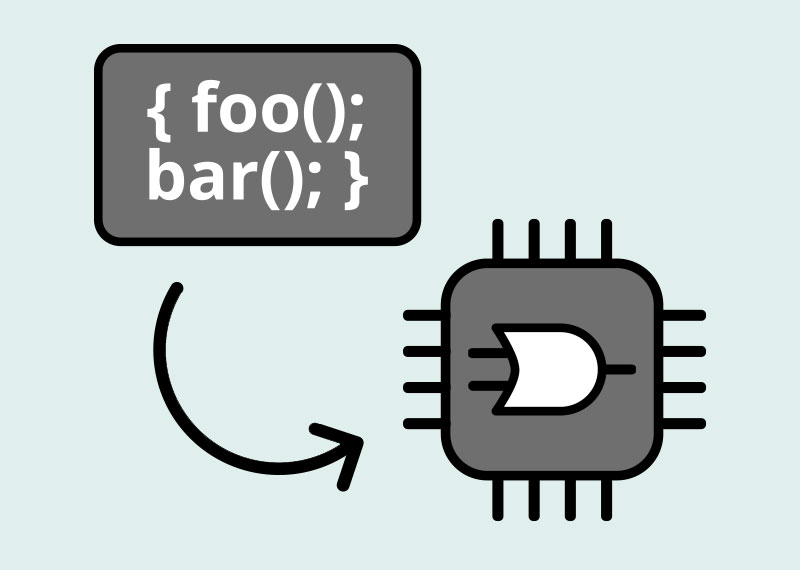

Die rechnerische Komplexität moderner KI-Algorithmen stellt für viele Computersysteme auch heute noch eine Herausforderung dar. Hardwarebeschleunigung für diese Algorithmen ist deshalb unerlässlich. Ein gegebenes neuronales Netz, bspw. im Standardformat ONNX, kann allerdings nicht direkt auf einem Hardwarebeschleuniger ausgeführt werden – es muss ein Mapping und Scheduling durchgeführt werden, um die Algorithmik auf die vorhandene Hardware abzubilden. Solche Werkzeuge sind für einfache Beschleuniger und bspw. für GPUs verfügbar, finden jedoch oft kein besonders gutes Mapping oder sind nicht auf unterschiedliche Beschleunigerdesigns anwendbar.

Aufgaben

Im Rahmen dieser Arbeit soll ein Mapping-Tool für einen adaptiven Hardwarebeschleuniger entwickelt werden. Aufbauend auf bestehenden Tools wie Apache TVM soll das entstehende Werkzeug in der Lage sein, für unterschiedliche Konfigurationen eines Beschleunigers gute Mappings zu finden. Der Beschleuniger liegt als FPGA-Design in HDL-Form vor und kann unterschiedlich konfiguriert und dimensioniert werden. Operationen, die vom Beschleuniger ggf. nicht unterstützt werden, können in Software auf einem RISC-V Prozessor ausgeführt werden. Als Teil der Literaturrecherche gilt es verschiedene Mapping-Tools aus Industrie und Wissenschaft auf ihre Eignung zu untersuchen sowie eine Auswahl an neuronalen Netzen zusammenzustellen, anhand deren der Ansatz getestet werden kann.

Voraussetzungen

- Interesse an der hardwarenahen Softwareentwicklung und Arbeit mit FPGA-Prototyping-Boards sowie an der Entwicklung von Compilern wie TVM

- Kenntnisse in Python & C++ zur Einarbeitung in bestehende Softwareprojekte

- Grundkenntnisse in HDL (VHDL/Verilog) von Vorteil