Fabian Lesniak, M.Sc.

- Wissenschaftlicher Mitarbeiter

- Gruppe: Prof. Becker

- Raum: 226.1

CS 30.10 - Tel.: +49 721 608-42504

- fabian lesniak ∂does-not-exist.kit edu

Engesserstr. 5

76131 Karlsruhe

Design von heterogenen Manycore-Plattformen

Während die Leistungsanforderungen an integrierte Schaltungen ständig steigen, kämpft die Halbleiterindustrie damit, mit diesen Anforderungen Schritt zu halten. Probleme mit der Leistungsdichte und statischen Leckagen traten in den Vordergrund, während frühere Effekte wie Dennard Scaling ausfielen. Um weitere Leistung zu gewinnen, wird stattdessen die Anzahl der Prozessorkerne erhöht. Solche Manycore-Systeme mit Hunderten von Prozessoren erfordern ein anderes Hardwaredesign als klassische eingebettete Systeme. Auch die Programmierbarkeit solcher Systeme unterscheidet sich stark, da Probleme in hohem Maße parallelisiert werden müssen.

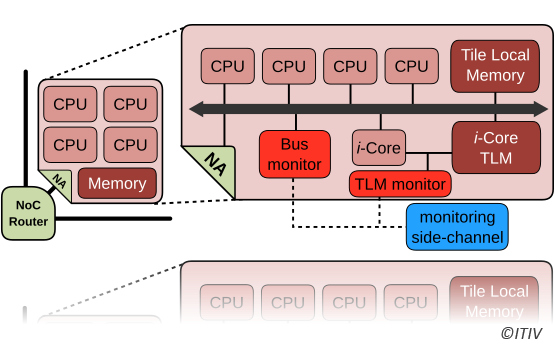

Laufzeitadaptive Architekturen

Ein modernes System on Chip muss Chipfläche und Leistung sparen, um das Design von kleinen, mobilen Geräte mit langer Batterielebensdauer zu ermöglichen. Dennoch erwarten die Nutzer eine sehr hohe Rechenleistung für sehr spezifische Probleme, wie die Verarbeitung von Medien oder die Inferenz neuronaler Netze. Durch die Entwicklung von Hardware-Architekturen, die während der Laufzeit rekonfigurierbar sind, werden sie vielseitiger und sogar zukunftssicher für Anwendungsfälle, die zum Zeitpunkt der Entwicklung noch nicht bekannt sind – bei kleinerer Chipfläche und weniger Dark Silicon Effekten. Bei der Entwicklung solcher adaptiven Hardware-Architekturen müssen verschiedene Designparameter sorgfältig abgewogen werden, damit das System für möglichst viele Zwecke geeignet ist.

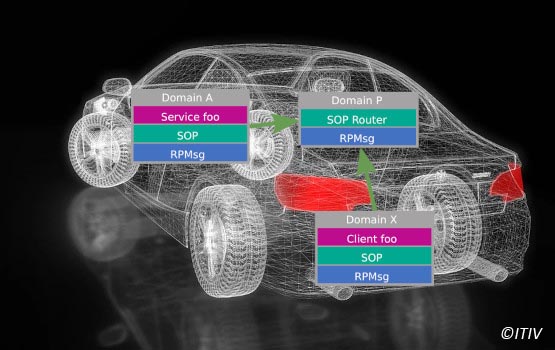

Hypervisor-basierte Systeme for sicherheitskritische Anwendungen

Sicherheitskritische Anwendungen findet man insbesondere im Bereich von Steuerung und Regelung von Fahrzeugen und Anlagen. Solche Systeme sind aufwändig zu entwickeln und zu pflegen, da eine einwandfreie Funktionalität garantiert werden muss – auch nach einem Update. Indem moderne Virtualisierungstechnologien eingesetzt werden, kann die Isolation einzelner Systemkomponenten verbessert werden. Dadurch wird die Komplexität des Gesamtsystems erhöht und eine Beurteilung der Sicherheit wird aufwändiger. Ziel der Forschung ist, die Hürden für den Einsatz eines Hypervisors in diesen Bereichen zu verringern.

| Titel | Typ |

|---|---|

| Entwicklung eines Mapping-Tools für adaptive KI-Beschleuniger | Masterarbeit |

| Modellierung eines KI-Beschleunigers zur Entwurfsraumexploration | Bachelorarbeit |

| Titel |

|---|

| Aufbau und Weiterentwicklung eines Demonstrators für Over The Air Updates auf hochautomatisierten Fahrzeugen |

Betreute studentische Arbeiten (Auswahl)

- MA: "Verteiltes Echtzeit-Monitoring von Manycores"

- MA: "Design eines prozessorbasierten Near-Memory-Beschleunigers"

- MA: "Entwicklung eines dynamischen und flexiblen Speichercontrollers für Manycore-Prototypen"

- MA: "Channel Estimation of Dynamic Intra-Tile Reallocatable Cache in Homogeneous GPPs"

- MA: "Hypervisor-Gastüberwachung in Safety-Critical Systems"

- MA: "Implementing an AI Accelerator as a Special Instruction"

- BA: "ARM-Debugger für den Xen-Hypervisor"

- BA: "Implementierung eines approximativen Beschleunigers"

- BA: "Dynamische CNN-Beschleunigung für den i-Core Prozessor"

Publikationen

Lesniak, F.; Gutermann, A.; Harbaum, T.; Becker, J.

2024. GLSVLSI ’24: Proceedings of the Great Lakes Symposium on VLSI 2024, 151 – 157, Association for Computing Machinery (ACM). doi:10.1145/3649476.3658737

Lesniak, F.; Harbaum, T.; Becker, J.

2024. 2023 IEEE 16th International Symposium on Embedded Multicore/Many-core Systems-on-Chip (MCSoC), Singapur, 18th - 21st December 2023, 340–346, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/MCSoC60832.2023.00057

Anantharajaiah, N.; Lesniak, F.; Harbaum, T.; Becker, J.

2023. 2023 IEEE 16th International Symposium on Embedded Multicore/Many-core Systems-on-Chip (MCSoC), 38 – 44, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/MCSoC60832.2023.00014

Lesniak, F.; Harbaum, T.; Becker, J.

2023. 2023 IEEE 36th International System-on-Chip Conference (SOCC), Santa Clara, USA, 05-08 September 2023, 1–6, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC58585.2023.10257090

Anantharajaiah, N.; Xu, Y.; Lesniak, F.; Harbaum, T.; Becker, J.

2023. IEEE Computer Society Annual Symposium on VLSI (ISVLSI), 1–6, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/ISVLSI59464.2023.10238569

Lesniak, F.; Anantharajaiah, N.; Harbaum, T.; Becker, J.

2023. RAPIDO ’23: Proceedings of the DroneSE and RAPIDO: System Engineering for constrained embedded systems, 31–38, Association for Computing Machinery (ACM). doi:10.1145/3579170.3579262

Guissouma, H.; Hohl, C. P.; Lesniak, F.; Schindewolf, M.; Becker, J.; Sax, E.

2022. IEEE Access, 10, 57696–57717. doi:10.1109/ACCESS.2022.3176879

Masing, L.; Lesniak, F.; Becker, J.

2021. IEEE embedded systems letters, 13 (1). doi:10.1109/LES.2020.2995084

Lesniak, F.; Kreß, F.; Becker, J.

2021. Applied Reconfigurable Computing. Ed.: S. Derrien, 221–231, Springer Nature Switzerland. doi:10.1007/978-3-030-79025-7_15

Anantharajaiah, N.; Kempf, F.; Masing, L.; Lesniak, F. M.; Becker, J.

2019. Proceedings of the 12th International Workshop on Network on Chip Architectures (NoCArc 2019), Columbus, OH, Ocober 12-13, 2019, 1–6, Association for Computing Machinery (ACM). doi:10.1145/3356045.3360718

Masing, L.; Lesniak, F.; Becker, J.

2019. 15th International Symposium on Applied Reconfigurable Computing, ARC 2019; Darmstadt; Germany; 9 April 2019 through 11 April 2019, 319–333. doi:10.1007/978-3-030-17227-5_23

Werner, S.; Masing, L.; Lesniak, F.; Becker, J.

2015. 2015 25th International Conference on Field Programmable Logic and Applications (FPL), London, United Kingdom, 2–4 September 2015, Art.Nr. 7294020, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/FPL.2015.7294020