Modellierung eines KI-Beschleunigers zur Entwurfsraumexploration

- Forschungsthema:KI-Beschleuniger, Hardwaremodellierung

- Typ:Bachelorarbeit

- Datum:ab 06 / 2023

- Betreuung:

Modellierung eines KI-Beschleunigers zur Entwurfsraumexploration

Kontext

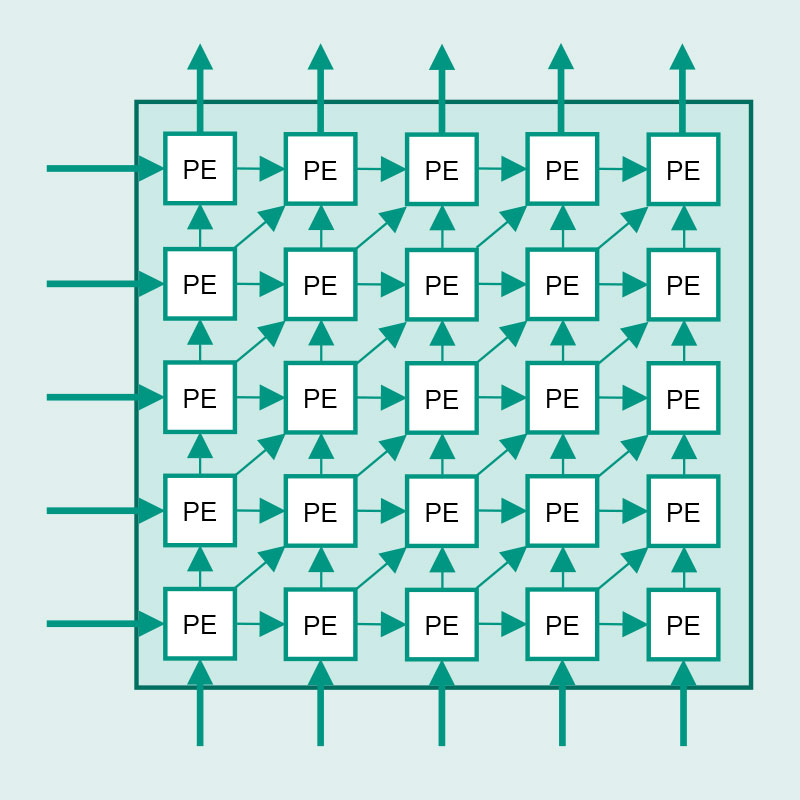

Für viele moderne Anwendungen sind spezialisierte Hardwarebeschleuniger nötig um eine ausreichende Verarbeitungsgeschwindigkeit zu erreichen. Insbesondere moderne KI-Ansätze profitieren von dedizierten Beschleunigern – doch die Dimensionierung hängt stark vom Anwendungsfall ab. Eine hohe Leistung wird durch viele parallele Verarbeitungseinheiten erreicht, in Embedded-Systemen ist jedoch nur eine kleine Chipfläche verfügbar. Mittels Performance-Modellen kann die Leistung von unterschiedlichen Ausprägungen eines Hardwaremoduls mit geringem Aufwand geschätzt werden und die Anwendbarkeit auf unterschiedliche neuronale Netze geprüft werden.

Aufgaben

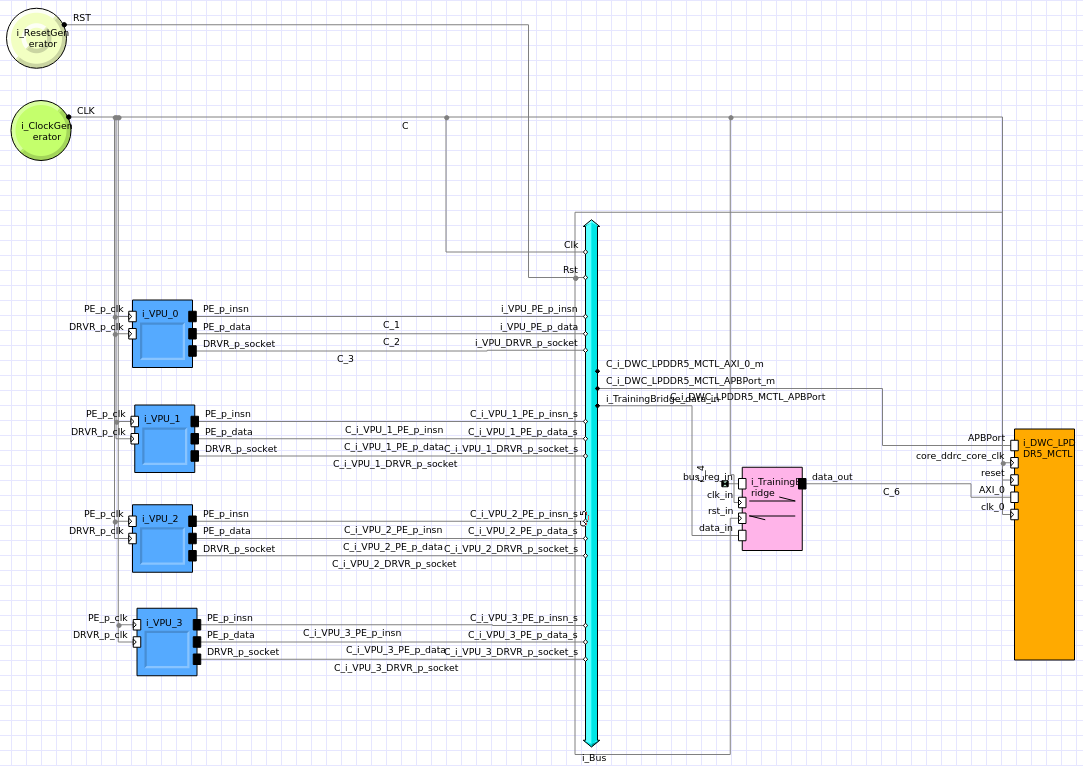

Im Rahmen dieser Arbeit soll ein Performanz-Modell eines bestehenden CNN-Beschleuniger-Designs in SystemC erarbeitet werden. Anhand dieses Modells wird mit gängigen Tools aus der Halbleiterindustrie (Synopsys Platform Architect) eine Entwurfsraumexploration durchgeführt, wodurch die Leistung unterschiedlicher Ausführungen des Beschleunigers beurteilt wird. Zur Evaluation des Modells werden verschiedenartige neuronale Netze auf ihre Leistungsanforderungen untersucht und das Verhalten des Modells analysiert. Abschließend können Empfehlungen abgegeben werden, welche Designparameter (Anzahl Einheiten, Puffergrößen, etc.) für bestimmte Netzte optimal sind.

Voraussetzungen

- Interesse am Design von Hardwarebeschleunigern und SoCs

- Vorkenntnisse in VHDL/Verilog sowie C

- Motivation und Interesse am selbstständigen Lösen von technischen Problemen