Julian Höfer, M.Sc.

- Wissenschaftlicher Mitarbeiter

- Gruppe: Prof. Becker

- Raum: 217

CS 30.10 - Tel.: +49 721 608-41310

- julian hoefer ∂does-not-exist.kit edu

- Engesserstr. 5

76131 Karlsruhe

Absicherung von KI-Methoden und Beschleunigern im sicherheitskritischen Umfeld

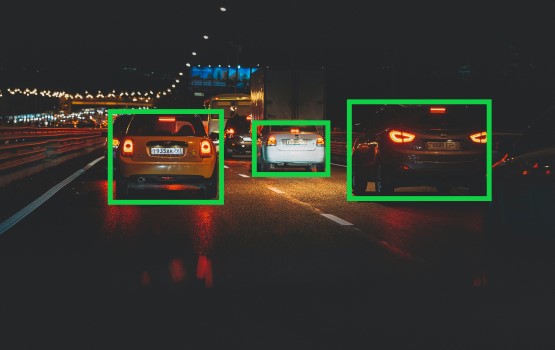

Die Grundlage für autonomes Fahren und weitere sicherheitskritische Anwendungen ist die zuverlässige Erkennung der unmittelbaren Umgebung mithilfe von Kameras, sowie Radar- und Lidarsensoren. Die besten Ergebnisse zur Objekterkennung liefert hier maschinelles Lernen, z.B. Convolutional Neural Networks. Die Herausforderung besteht akut darin, diese neuronalen Netze in eingebettete Systeme zu integrieren und dabei die Zuverlässigkeit sicherzustellen. Insbesondere zufällige Hardwarefehler sowie die Unfähigkeit, die eigene Unsicherheit zu schätzen, verhindern noch den sicherheitskritischen Einsatz.

KI-Akzelerator – Algorithmus Co-Design und Entwurfsraumexploration

Mit der wachsenden Zahl an Einsatzmöglichkeiten für maschinelles Lernen steigen nicht nur die Anforderungen im Hinblick auf algorithmische Genauigkeit, sondern auch im Hinblick auf die Implementierung in die Hardware. Wichtige Ziele sind die Minimierung des Speicherbedarfs und die Reduktion des Energieverbrauchs. Optimierungen sind hierbei auf algorithmischer Ebene, als auch auf Hardwarearchitekturebene möglich und müssen gegenseitig für die jeweilige Anwendung abgewogen werden. Hierbei erzielen Co-Design Methoden und die zielgerichtete Exploration des Entwurfsraums die besten Ergebnisse.

Energieeffiziente KI-Hardwarebeschleuniger

Maschinelles Lernen kann heutzutage bereits komplexe Probleme in Bildverarbeitung für autonomes Fahren, Industrieautomatisierung oder Fehlererkennung gut lösen. Ein Nachteil solcher Systeme bleibt nach wie vor der hohe Rechenaufwand und damit verbundene Energiebedarf. Aus diesem Grund werden sowohl in der Forschung, als auch in der Industrie (Google, Tesla, …) spezielle Hardwarearchitekturen entwickelt, um die Algorithmen effizient zu implementieren. Auch wir arbeiten im Team an neuen Konzepten und Ideen der Hardwarebeschleunigung im Bereich des maschinellen Lernens.

| LVNr. | Titel | Typ | Semester |

|---|---|---|---|

| 2311617 | Übungen zu 2311615 Digitaltechnik / Grundlagen der Digitaltechnik | Übung (Ü) | WS 25/26 |

| 2311170 | Tutorien zu 2311615 Digitaltechnik / Grundlagen der Digitaltechnik | Tutorium (Tu) | WS 23/24 |

Betreute studentische Arbeiten (Auswahl)

- BA: „Robustness of Systolic Arrays in Regards to Partial Failures of Computation Units“

- MA: „Modelling and Simulation of Built-in self-test Concepts for Hardware Defect Detection on AI Accelerators“

- BA: „Evaluation of Methods for Sampling-based Uncertainty Estimation in Deep Learning-based Object Detection“

Publikationen

Mojumder, S.; Friedrich, S.; Matúš, E.; Lüders, M.; Friedrich, M.; Renke, O.; Blume, H.; Kock, M.; Schewior, G.; Grantz, D.; Benndorf, J.; Hoefer, J.; Schmidt, P.; Becker, J.; Fasfous, N.; Mori, P.; Vögel, H.-J.; Ahmadifarsani, S.; Kontopoulos, L.; Schlichtmann, U.; Li, Y.-J.; Fettweis, G. P.

2025. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 33 (11), 2961–2974. doi:10.1109/TVLSI.2025.3603887

Hoefer, J.; Lesniak, F. M.; Gutermann, A.; Wöran, F.; Harbaum, T.; Becker, J. E.

2025. 2025 IEEE 38th International System-on-Chip Conference (SOCC), Dubai, 29th September 2025 - 1st October 2025, 1–6, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC66126.2025.11235419

Karle, C.; Fuerst-Walter, I.; Schade, F.; Hoefer, J.; Lesniak, F.; Harbaum, T.; Becker, J.

2025. 2025 IEEE 4th German Education Conference (GECon), Hamburg, 21st-23rd July 2025, 1–5, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/GECon64629.2025.11369364

Tahoori, M.; Meyers, V.; Sadeghipour Roodsari, M.; Xu, H.; Becker, J.; Harbaum, T.; Frombach, F.; Hoefer, J.; Sotiropoulos, G.; Henkel, J.; Demirdag, Z.; Khdr, H.; Nassar, H.; Schlichtmann, U.; Geier, J.; van Kempen, P.; Sigl, G.; Koegler, S.; Probst, M.; Teich, J.; Hannig, F.; Sabih, M.; Sesli, B.; Wehn, N.; Steiner, L.; Kunz, W.; Shelkamy Ali, M.

2025. Proceedings of the International Conference on Hardware/Software Codesign and System Synthesis; Taipeh, Taiwan, 28.09.-03.10.2025, 23–32, Association for Computing Machinery (ACM). doi:10.1145/3742873.3756928

Hoefer, J.; Schmidt, P.; Toto-Kiesa, H.; Hoefer, S.; Schewior, G.; Engelke, D.; Eickel, K.-H.; Grantz, D.; Harbaum, T.; Becker, J.

2025. Proceedings of the Great Lakes Symposium on VLSI 2025, 704–711, Association for Computing Machinery (ACM). doi:10.1145/3716368.3735208

Kreß, F.; Hoefer, J.; Lin, Q.; Schmidt, P.; Zhu, Z.; Zhu, Y.; Harbaum, T.; Wang, Y.; Becker, J.

2025. 2025 26th International Symposium on Quality Electronic Design (ISQED), 23rd-24th April 2025, San Francisco, 1–8, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/ISQED65160.2025.11014471

Mojumder, S.; Friedrich, S.; Matúš, E.; Fettweis, G.; Lueders, M.; Friedrich, M.; Renke, O.; Blume, H.; Hoefer, J.; Schmidt, P.; Becker, J.; Grantz, D.; Kock, M.; Benndorf, J.; Fasfous, N.; Mori, P.; Voegel, H.-J.; Ahmadifarsani, S.; Kontopoulos, L.; Schlichtmann, U.; Bierzynski, K.

2024. 2024 IEEE Nordic Circuits and Systems Conference (NorCAS), Lund, Sweden, 29-30 October 2024, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/NorCAS64408.2024.10752454

Hoefer, J.; Stammler, M.; Kreß, F.; Hotfilter, T.; Harbaum, T.; Becker, J.

2024. IEEE International Symposium on Defect and Fault Tolerance in VLSI and Technologisch Systems (DFT), Didcot, United Kingdom, 08-10 October 2024, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/DFT63277.2024.10753546

Stammler, J. M.; Hoefer, J.; Schmidt, P.; Harbaum, T.; Becker, J.

2024. 2024 IEEE Computer Society Annual Symposium on VLSI (ISVLSI), 656 – 660, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/ISVLSI61997.2024.00125

Neu, M.; Karle, C.; Schmidt, P.; Höfer, J.; Harbaum, T.; Becker, J.

2024. IEEE 37th International System-on-Chip Conference (SOCC 2024), 6 S., Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC62300.2024.10737798

Kreß, F.; Serdyuk, A.; Kobsar, D.; Hotfilter, T.; Höfer, J.; Harbaum, T.; Becker, J.

2024. 2024 IEEE 37th International System-on-Chip Conference (SOCC), Dresden, Germany, 16-19 September 2024, 126–131, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC62300.2024.10737863

Kreß, F.; El Annabi, E. M.; Hotfilter, T.; Hoefer, J.; Harbaum, T.; Becker, J.

2024. 2024 IEEE Computer Society Annual Symposium on VLSI (ISVLSI), 1st-3rd July 2024, Knoxville, 39–44, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/ISVLSI61997.2024.00019

Hoefer, J.; Gauß, M.; Adams, M.; Kreß, F.; Kempf, F.; Karle, C.; Harbaum, T.; Barth, A.; Becker, J.

2024. 2024 IEEE International Symposium on Circuits and Systems (ISCAS), Singapore, Singapore, 19-22 May 2024, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/ISCAS58744.2024.10557955

Stammler, M.; Höfer, J.; Kraus, D.; Schmidt, P.; Hotfilter, T.; Harbaum, T.; Becker, J.

2023. Procedia Computer Science, 222, 499 – 508. doi:10.1016/j.procs.2023.08.188

Kreß, F.; Sidorenko, V.; Schmidt, P.; Hoefer, J.; Hotfilter, T.; Walter, I.; Harbaum, T.; Becker, J.

2023. Computer Networks, 229, Article no: 109759. doi:10.1016/j.comnet.2023.109759

Vögel, H.-J.; Becker, J.; Benndorf, J.; Bierzynski, K.; Blume, H.; Fettweis, G.; Friedrich, M.; Friedrich, S.; Grantz, D.; Höfer, J.; Kempf, F.; Lueders, M.; Teepe, G.

2023. MikroSystemTechnik Kongress 2023; Kongress, 889–894, VDE Verlag

Kempf, F.; Hoefer, J.; Harbaum, T.; Becker, J.; Fasfous, N.; Frickenstein, A.; Voegel, H.-J.; Friedrich, S.; Wittig, R.; Matúš, E.; Fettweis, G.; Lueders, M.; Blume, H.; Benndorf, J.; Grantz, D.; Zeller, M.; Engelke, D.; Eickel, K.-H.

2023. 2023 Design, Automation & Test in Europe Conference & Exhibition (DATE), Antwerp, Belgium, 17-19 April 2023, Institute of Electrical and Electronics Engineers (IEEE). doi:10.23919/DATE56975.2023.10137257

Kreß, F.; Serdyuk, A.; Hiegle, M.; Waldmann, D.; Hotfilter, T.; Hoefer, J.; Hamann, T.; Barth, J.; Kämpf, P.; Harbaum, T.; Becker, J.

2023. 26th Euromicro Conference on Digital System Design (DSD 2023), 569–576, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/DSD60849.2023.00084

Kempf, F.; Höfer, J.; Hotfilter, T.; Becker, J.

2023. 2023 IEEE 16th International Symposium on Embedded Multicore/Many-core Systems-on-Chip (MCSoC), 276 – 283, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/MCSoC60832.2023.00048

Hotfilter, T.; Hoefer, J.; Merz, P.; Kreß, F.; Kempf, F.; Harbaum, T.; Becker, J.

2023. 2023 IEEE 36th International System-on-Chip Conference (SOCC), Santa Clara, USA, 05-08 September 2023, 1–6, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC58585.2023.10256738

Hoefer, J.; Hotfilter, T.; Kreß, F.; Qiu, C.; Harbaum, T.; Becker, J.

2023. Computer Vision Systems – 14th International Conference, ICVS 2023, Vienna, Austria, September 27–29, 2023. Ed.: H. Christensen, 299–309, Springer Nature Switzerland. doi:10.1007/978-3-031-44137-0_25

Hotfilter, T.; Höfer, J.; Kreß, F.; Kempf, F.; Kraft, L.; Harbaum, T.; Becker, J.

2023. 2023 IEEE 5th International Conference on Artificial Intelligence Circuits and Systems (AICAS), 1–5, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/AICAS57966.2023.10168566

Hoefer, J.; Kempf, F.; Hotfilter, T.; Kreß, F.; Harbaum, T.; Becker, J.

2023. Proceedings of the Great Lakes Symposium on VLSI 2023, 287–292, Association for Computing Machinery (ACM). doi:10.1145/3583781.3590226

Hotfilter, T.; Schmidt, P.; Höfer, J.; Kreß, F.; Harbaum, T.; Becker, J.

2023. DroneSE and RAPIDO: System Engineering for constrained embedded systems, 73–78, Association for Computing Machinery (ACM). doi:10.1145/3579170.3579258

Kreß, F.; Hoefer, J.; Hotfilter, T.; Walter, I.; El Annabi, E. M.; Harbaum, T.; Becker, J.

2023. Machine Learning and Principles and Practice of Knowledge Discovery in Databases. Hrsg.: I. Koprinska. Pt. 1, 557–568, Springer International Publishing. doi:10.1007/978-3-031-23618-1_37

Kempf, F.; Höfer, J.; Kreß, F.; Hotfilter, T.; Harbaum, T.; Becker, J.

2022. Conference Proceedings: 2022 IEEE 35th International System-on-Chip Conference (SOCC) Ed.: S. Sezer, 1–6, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC56010.2022.9908110

Kreß, F.; Hoefer, J.; Hotfilter, T.; Walter, I.; Sidorenko, V.; Harbaum, T.; Becker, J.

2022. 18th International Conference on Distributed Computing in Sensor Systems (DCOSS), 133–140, IEEEXplore. doi:10.1109/DCOSS54816.2022.00034

Kreß, F.; Serdyuk, A.; Hotfilter, T.; Höfer, J.; Harbaum, T.; Becker, J.; Hamann, T.

2022. 2022 11th Mediterranean Conference on Embedded Computing (MECO). Ed.: IEEE, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/MECO55406.2022.9797131

Fasfous, N.; Vemparala, M. R.; Frickenstein, A.; Valpreda, E.; Salihu, D.; Höfer, J.; Singh, A.; Nagaraja, N.-S.; Voegel, H.-J.; Vu Doan, N. A.; Martina, M.; Becker, J.; Stechele, W.

2022. Proceedings of the 2022 Design, Automation & Test in Europe Conference & Exhibition (DATE 2022). Ed.: C. Bolchini, 238–243, Institute of Electrical and Electronics Engineers (IEEE). doi:10.23919/DATE54114.2022.9774574

Walter, I.; Ney, J.; Hotfilter, T.; Rybalkin, V.; Hoefer, J.; Wehn, N.; Becker, J.

2022. Machine Learning and Principles and Practice of Knowledge Discovery in Databases – International Workshops of ECML PKDD 2021, Virtual Event, September 13-17, 2021, Proceedings, Part I. Ed.: M. Kamp, 339–350, Springer International Publishing. doi:10.1007/978-3-030-93736-2_26

Hotfilter, T.; Hoefer, J.; Kreß, F.; Kempf, F.; Becker, J.

2021. IEEE 34th International System-on-Chip Conference (SOCC), 14th-17th September 2021, Las Vegas, Nevada, USA, 83–88, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC52499.2021.9739212

Fasfous, N.; Vemparala, M.-R.; Frickenstein, A.; Badawy, M.; Hundhausen, F.; Höfer, J.; Nagaraja, N.-S.; Unger, C.; Vögel, H.-J.; Becker, J.; Asfour, T.; Stechele, W.

2021. 2021 IEEE International Conference on Robotics and Automation (ICRA): 30 May – 5 June 2021, Xi’an, China, 13430–13437, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/ICRA48506.2021.9561045