ReLiSys

- Ansprechperson:

- Projektgruppe:

Prof. Becker

- Förderung:

ZIM des Bundesministeriums für Wirtschaft und Klimaschutz (BMWK)

FKZ: ZF4011810DH9 (KIT)

- Projektbeteiligte:

Wibu-Systems AG, emmtrix Technologies GmbH, Forschungszentrum Informatik (FZI), KIT (ITIV & CES)

- Starttermin:

01.01.2020

- Endtermin:

30.06.2022

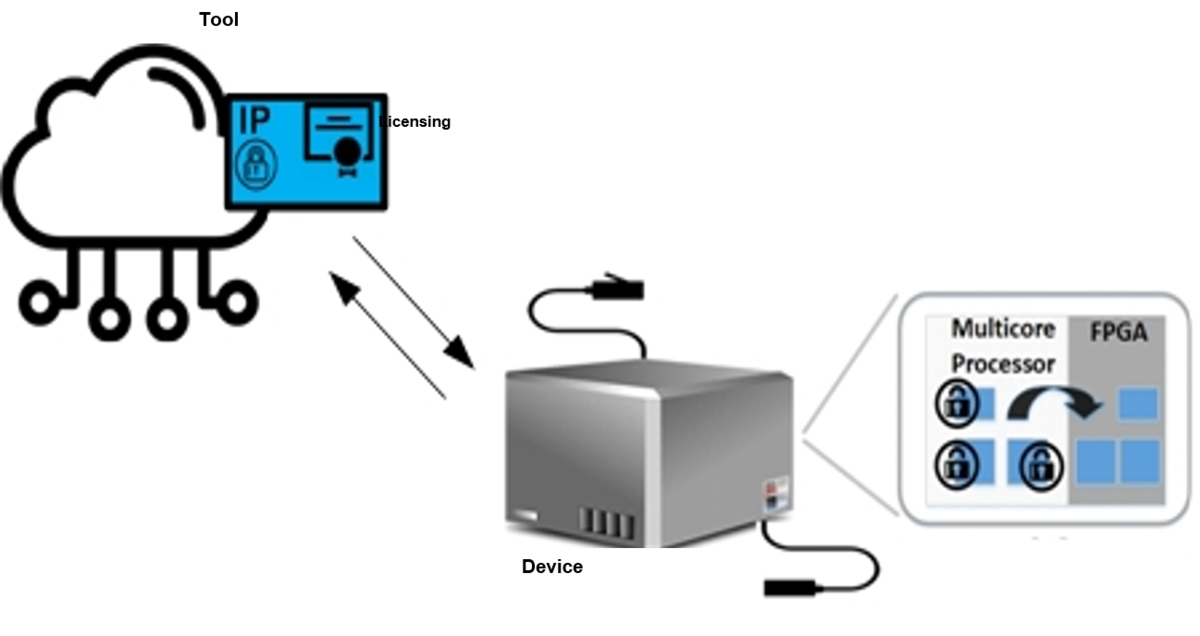

ReLiSys – Remote Configuration of Licensable-IP in FPGA Systems

![]()

Projektziele

Die Projektziele reichen von der Entwicklung eines "Independent IP Generation Framework" über die Entwicklung eines "Flow for Establishing Trust on a Device" bis hin zur Analyse von Angriffen wie Seitenkanalangriffen und Trojaner-Infektionen in IP-Cores, einschließlich der Entwicklung von Gegenmaßnahmen für diese Angriffe. Es wird ein Tool entwickelt, das die EDA-Tools der FPGA-Anbieter nutzt, um ein Standard-Basisdesign zu erstellen, das von mehreren an der IP-Core-Lizenzierung beteiligten Parteien verwendet werden kann. Mehrere Core-Anbieter (CVs) von IP-Cores und der Systementwickler (SD) eines Geräts können das Tool gemeinsam nutzen, um IP-Cores zu erstellen, die auf dem Gerät interoperabel sind, ohne dass sie sich gegenseitig preisgeben. Das Zielgerät, das FPGA, kann durch verschiedene Angriffe für IP-Diebstahl anfällig sein. Die Angriffe auf ein Gerät werden analysiert und entsprechende Gegenmaßnahmen entwickelt, um eine Vertrauensbildung auf einem Gerät zu schaffen.

Darüber hinaus stellt das Framework sicher, dass IPs nur auf den Geräten auf der Tool-Ebene konfiguriert werden können, für die sie vom CV lizenziert wurden, indem ein Pay-per-Device-Lizenzierungsschema implementiert wird. Darüber hinaus sind weitere Features implementiert, wie z. B. Gegenmaßnahmen für Seitenkanalangriffe (SCAs) und Trojaner-Erkennung am Gerät.

ITIV Beteiligung

ITIV beteiligt sich hauptsächlich an der Definition der Sicherheitsanforderungen des Ablaufs zum Herstellen von Vertrauen auf einem Gerät, zum Implementieren der Trojaner-Erkennung und zum Integrieren der Erkennung in das Gerät. Das Trojaner-Erkennungsmodul kann dem CV-Tool oder dem sicheren Betriebssystem des Multicore-Prozessors (CPU) des Zielgeräts hinzugefügt werden. Ein teilweise rekonfigurierbarer IP-Core mit oder ohne Trojaner-Einfügung auf Tool-Ebene ist die primäre Quelle für die Trojaner-Erkennung im Tool oder Gerät.