PARFAIT II

- Ansprechperson:

- Projektgruppe:

Prof. Becker

- Förderung:

DFG

- Projektbeteiligte:

KIT, NaMLab, TU Darmstadt

- Starttermin:

01.02.2022

- Endtermin:

31.01.2025

PARFAIT II - Poweraware AmbipolaR Fpga ArchITecture II

Projektziele

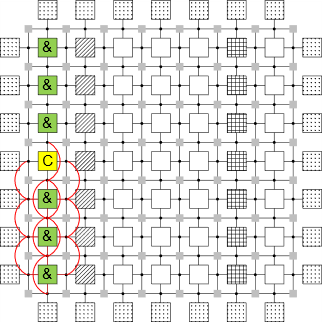

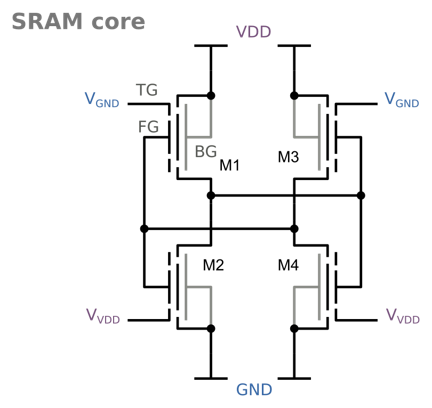

In PARFAIT II werden planare rekonfigurierbare Feldeffekttransistoren (RFETs) mit elektrisch einstellbarer p- und n-Leitfähigkeit erforscht. Der Schwerpunkt von PARFAIT II liegt auf der Herstellung der Transistoren, der Entwicklung von Logikgattern und deren Einsatz in komplexen Schaltungen. Hierfür muss ein zuverlässiger und reproduzierbarer Herstellungsprozess für planare RFETs entworfen werden. Nach einer gemeinsamen Spezifikationsphase werden die Simulationsmodelle aus PARFAIT I durch Entwurf, Fertigung und Messung von Testschaltungen verifiziert und an reale Fertigungsbedingungen angepasst. Damit werden die Grundlagen geschaffen, um rekonfigurierbare Transistoren in realen Anwendungen mit skalierten Geometrien in größerem Maßstab einsetzen zu können. Darüber hinaus werden in PARFAIT II Anwendungen auf Schaltungs- und Systemebene untersucht, für die die simulierten und gemessenen Eigenschaften der untersuchten RFETs am vielversprechendsten sind. Ein wichtiger Teil des Projekts ist die Untersuchung des Temperaturverhaltens der RFETs von der Technologie- bis zur Systemebene.

ITIV Beteiligung

Das ITIV wird die dynamische Kompensation von PVT- und Alterungseffekten auf Schaltkreis- und Systemebene untersuchen, insbesondere für eine auf RFETs basierende FPGA-Architektur: Nach Messungen der Ausbreitungsverzögerungen wird die Fähigkeit der planaren RFETs genutzt, Schwellenspannungen, Leckströme und Schaltströme von Zellen über das zusätzliche Back-Gate feinkörnig anzupassen, unabhängig von der konfigurierten Logikfunktion (eingestellt über die Front-Gates).