M. Sc. Maximilian Kirschner

- ESS/ Wissenschaftlicher Mitarbeiter

- Gruppe: Prof. Becker

- Tel.: +49 721 9654 186

- kirschner ∂does-not-exist.fzi de

- www.fzi.de/team/maximilian-kirschner/

Forschungszentrum Informatik (FZI)

Haid- und Neu-Str. 10 - 14

76131 Karlsruhe

Zeitvorhersagbare Hardware Architekturen

Das Hauptziel von zeitvorhersagbarer Hardware besteht darin, die zeitlichen Eigenschaften und ein deterministisches Verhalten des Systems zu garantieren, um Echtzeitanforderungen zu erfüllen. Dabei gilt es vor allem sogenannte Timing-Anomalien zu vermeiden. Auf Vorhersagbarkeit optimierte Hardware bietet oft eine geringere Peak-Performance oder einen eingeschränkten Funktionsumfang. Die Verwendung zeitvorhersagbarer Hardware ist vor allem in Anwendungsfeldern sinnvoll, in denen Reaktionszeiten kritisch sind (z.B. automatisiertes Fahren, Robotik oder Luft- und Raumfahrt).

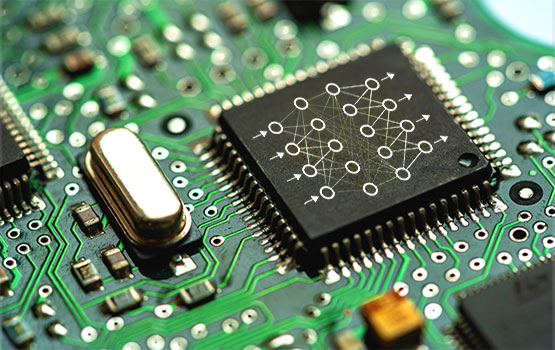

Künstliche Intelligenz in eingebetteten Systemen

Die Integration von künstlicher Intelligenz in eingebettete Systeme bietet mehrere Vorteile: Die Modelle sind oft auf begrenzte Ressourcen optimiert, was vor allem in Bezug auf Energieverbrauch in batteriebetriebenen Geräten vorteilhaft ist. Die lokale Verarbeitung von Sensordaten reduziert die Latenz, was vor allem in Anwendungen des automatisierten Fahrens oder der Robotik notwendig ist, da hier schnelle Reaktionen entscheidend sind. Die größte Herausforderung dabei besteht in der immer weiter steigenden Modellgröße und Komplexität aktueller KI-basierter Anwendungen.

Compiler und Tools zur Abschätzung der Worst-Case Execution Time

In echtzeitkritischen Domänen ist es für ein gegebenes Programm wichtig, abzuschätzen, wie lange dessen Ausführung im schlimmsten Fall dauert(Worst-Case Execution Time, WCET). Die Abschätzung der WCET erfolgt mittels Tools, welche die Hardware modellieren und den längst möglichen Pfad im Programm finden. Dieser längste Pfad hängt neben der Hardware und der Anwendung selbst auch vom verwendeten Compiler ab. Die WCET dient zum einen dazu sicherzustellen, dass harte zeitliche Grenzen eingehalten werden, zum anderen liefert die Analyse Anhaltspunkte für mögliche Optimierungen in der Anwendung.

| Titel | Typ | Datum |

|---|---|---|

| Hardware Beschleunigung von Optimierungsalgorithmen in nicht-linearer modellprädiktiver Regelung | Masterarbeit | ab 02 / 2024 |