Praktikum System-on-Chip

- Typ: Praktikum (P)

- Lehrstuhl: Institut für Technik der Informationsverarbeitung

- Semester: WS 25/26

-

Zeit:

wöchentlich montags 14:00 - 18:00 Uhr

ab dem 27.10.2025

bis zum 16.02.2026

in 30.10 ITIV Raum 216

30.10 Nachrichtentechnik, Institutsgebäude

-

Dozent:

Prof. Dr.-Ing. Dr. h.c. Jürgen Becker

Prof. Dr. Ivan Peric - SWS: 4

- LVNr.: 2311612

- Hinweis: Präsenz

| Vortragssprache | Deutsch |

| Organisatorisches | Mo 14:00-18:00, Geb. 30.10, Raum 216 |

Hinweis

Die Anmeldung für das Praktikum findet über ILIAS statt. Während unseres offiziellen Anmeldezeitraum vom 01. Oktober bis zum 18. Oktober können Sie sich über ILIAS für dieses Labor registrieren.

Bei organisatorischen Fragen melden Sie sich bitte bei Herr Serdyuk oder bei Herr Neu.

Praktikum System-on-Chip

Empfohlene Vorkenntnisse

- Kenntnisse im Verilog Entwurf, z.B. aus Design Digitaler Schaltkreise (2312683)

- Kenntnisse im Entwurf analoger Schaltungen (Verstärkerschaltungen, Stabilitätsbetrachtungen), z.B. aus Design analoger Schaltkreise (2312664)

- Kenntnisse im VHDL Entwurf, z.B. aus Hardware Modeling and Simulation (2311608)

- Kenntnisse in Simulation digitaler Schaltungen, z.B. aus Hardware Modeling and Simulation (2311608)

- Kenntnisse von Hardware Entwurfsprozessen und Algorithmen, z.B. aus Hardware-Synthese und -Optimierung (2311619)

Ziele

Die Studierenden können grundlegende Kenntnisse des digitalen und analogen Schaltungsentwurfs sowie der hardwarenahen Softwareprogrammierung wiedergeben. In der Praxis sind die Studierenden in der Lage anhand einer aktuellen System-on-Chip-Architektur diese Methoden in den folgenden Bereichen anzuwenden:

- Simulation der entworfenen Digital- und Analogschaltungen

- Debugging der Implementierungen auf Simulations- und Realisierungsebene

- Verifikation des entwickelten Gesamtsystems durch Testbenches

Darüber hinaus können sie den Ansatz des Hardware/Software-Codesigns anwenden und können Realisierungstargets anhand der gegebenen Anforderungen bewerten (FPGA und ASIC).

Inhalte

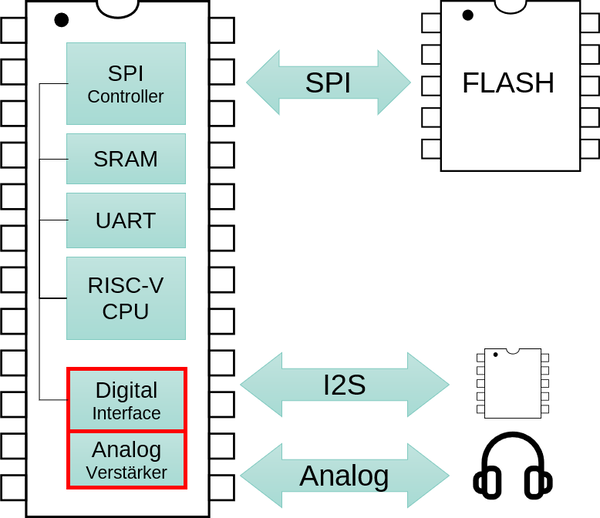

Im Praktikum System-on-Chip wird eine vollwertige Mixed-Signal-Hardwarearchitektur zur Audio-Wiedergabe auf Basis eines System-On-Chip (SoC) entwickelt.

Der Systementwurf umfasst dabei das Erstellen notwendiger Teilkomponenten, deren Integration in ein Gesamtsystem sowie die Simulation und Verifikation der individuellen Komponenten und des Gesamtsystems. Ein Prototyp wird auf FPGA-Basis implementiert und getestet. Anschließend wird die Integration für eine mögliche ASIC-Fertigung vorbereitet. Dabei werden auch Analog-Schaltungen betrachtet und entworfen, um einen Audio-Verstärker aufzubauen.