Tobias Dörr, M. Sc.

- Member of Scientific Staff

- Group: Prof. Becker

- Room: 218.1

- Phone: +49 721 608-41308

- tobias doerr ∂does-not-exist.kit edu

Engesserstr. 5

76131 Karlsruhe

Model-based design of safety-critical embedded systems

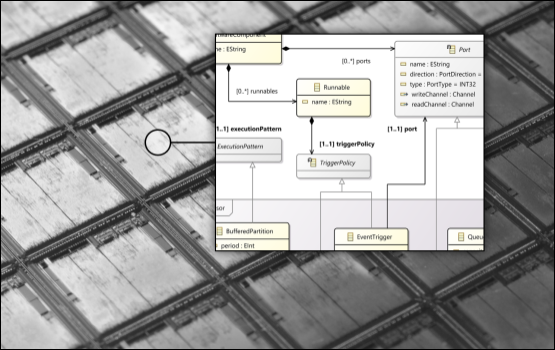

Modern embedded systems used in domains such as automotive or aerospace are subject to increasingly stringent safety and real-time requirements. To cope with the complexity that is associated with the development of such systems, novel design paradigms based on formal models are becoming increasingly important. In this context, we develop modeling techniques and, based on these techniques, software tools that automatically transform given model instances into reliable implementation artifacts.

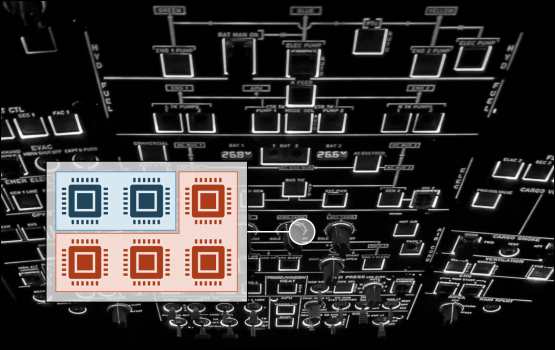

Synthesis of isolation mechanisms for modern mixed-criticality systems

To meet their performance requirements, modern embedded systems are increasingly based on multicore processors. This is often accompanied by a tight integration of subsystems with different criticality levels. To ensure that a sufficient degree of safety and security is achieved despite this integration, reliable isolation mechanisms must be incorporated into the systems. We investigate approaches that perform an automatic generation of such mechanisms by leveraging available hardware capabilities.

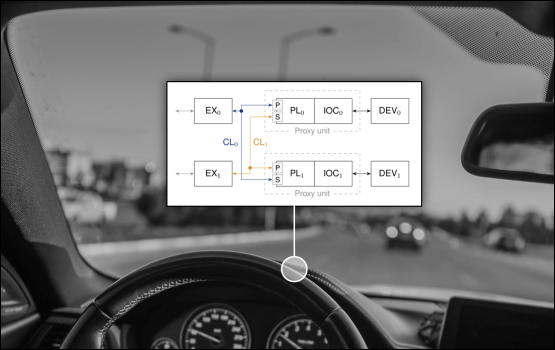

Fault tolerance mechanisms based on dynamic hardware redundancy

As automated driving functions are on the rise, the risk of electronic malfunctions in the vehicle leading to physical harm is increasing. Therefore, components that are relevant in this context must often be designed in such a way that they reliably deliver a defined minimum level of functionality despite such malfunctions. This requires the use of suitable fault tolerance mechanisms. We are researching how the concept of dynamic hardware redundancy can be used to implement such mechanisms a particularly cost-effective manner.

Publications

Schade, F.; Dörr, T.; Ahlbrecht, A.; Janson, V.; Durak, U.; Becker, J.

2024. 2023 26th Euromicro Conference on Digital System Design (DSD), Golem, 6th - 8th September 2023, 436 – 443, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/DSD60849.2023.00067

Dörr, T.; Schade, F.; Becker, J.

2023. Computer Safety, Reliability, and Security. Ed.: J. Guiochet, 181–195, Springer Nature Switzerland. doi:10.1007/978-3-031-40923-3_14

Dörr, T.; Schade, F.; Ahlbrecht, A.

2023, June 7. 4th Summer School on Cyber-Physical Systems and Internet-of-Things (CPS&IoT 2023), Budva, Montenegro, June 6–10, 2023

Dörr, T.; Schade, F.; Masing, L.; Becker, J.; Keramidas, G.; Antonopoulos, C. P.; Mavropoulos, M.; Kelefouras, V.; Voros, N.

2022. 2022 IEEE Computer Society Annual Symposium on VLSI (ISVLSI), Nicosia, Cyprus, 04-06 July 2022, 369–370, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/ISVLSI54635.2022.00081

Dörr, T.; Schade, F.; Ahlbrecht, A.; Zaeske, W.; Masing, L.; Durak, U.; Becker, J.

2022. 2022 IEEE/ACM 26th International Symposium on Distributed Simulation and Real Time Applications (DS-RT), 151–159, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/DS-RT55542.2022.9932069

Schade, F.; Dörr, T.; Becker, J.

2022. Conference Proceedings: 2022 IEEE 35th International System-on-Chip Conference (SOCC) Ed.: S. Sezer, 1–2, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC56010.2022.9908090

Siddiqui, F.; Khan, R.; Sezer, S.; McLaughlin, K.; Masing, L.; Dörr, T.; Schade, F.; Becker, J.; Ahlbrecht, A.; Zaeske, W.; Durak, U.; Adler, N.; Sailer, A.; Weber, R.; Wilhelm, T.; Nemeth, G.; Nemeth, G.; Morales, V.; Gomez, P.; Keramidas, G.; et al.

2022. 2022 IEEE 95th Vehicular Technology Conference: (VTC2022-Spring): Proceedings ; 19–22 June 2022, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/VTC2022-Spring54318.2022.9860859

Masing, L.; Dörr, T.; Schade, F.; Becker, J.; Keramidas, G.; Antonopoulos, C. P.; Mavropoulos, M.; Tiganourias, E.; Kelefouras, V.; Antonopoulos, K.; Voros, N.; Durak, U.; Ahlbrecht, A.; Zaeske, W.; Panagiotou, C.; Karadimas, D.; Adler, N.; Sailer, A.; Weber, R.; Wilhelm, T.; et al.

2022. 2022 Design, Automation & Test in Europe Conference & Exhibition (DATE), Antwerp, Belgium, 14-23 March 2022, 814–818, Institute of Electrical and Electronics Engineers (IEEE). doi:10.23919/DATE54114.2022.9774534

Dörr, T.; Sandmann, T.; Becker, J.

2021. Microprocessors and microsystems, 87, Article no: 104377. doi:10.1016/j.micpro.2021.104377

Dörr, T.; Sandmann, T.; Friederich, P.; Leitner, A.; Becker, J.

2021. Microprocessors and microsystems, 87, Aricle no: 104380. doi:10.1016/j.micpro.2021.104380

Becker, J.; Masing, L.; Dörr, T.; Schade, F.; Keramidas, G.; Antonopoulos, C. P.; Mavropoulos, M.; Tiganourias, E.; Kelefouras, V.; Antonopoulos, K.; Voros, N.; Durak, U.; Ahlbrecht, A.; Zaeske, W.; Panagiotou, C.; Karadimas, D.; Adler, N.; Sailer, A.; Weber, R.; Wilhelm, T.; et al.

2021. Proceedings 2021 31st International Conference on Field-Programmable Logic and Applications: FPL 2021 ; Dresden, Germany, 30 August – 3 September 2021, 382–383, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/FPL53798.2021.00075

Dörr, T.; Sandmann, T.; Mohr, H.; Becker, J.

2021. 2021 24th Euromicro Conference on Digital System Design (DSD), 107–114, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/DSD53832.2021.00026

Dörr, T.; Sandmann, T.; Friederich, P.; Leitner, A.; Becker, J.

2020. 2020 23rd Euromicro Conference on Digital System Design (DSD), 630–637, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/DSD51259.2020.00103

Dörr, T.; Sandmann, T.; Becker, J.

2020. 2020 23rd Euromicro Conference on Digital System Design (DSD), 596–603, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/DSD51259.2020.00098

Dörr, T.; Sandmann, T.; Schade, F.; Bapp, F. K.; Becker, J.

2019. Applied Reconfigurable Computing – 15th International Symposium, ARC 2019, Darmstadt, 9.-11. April 2019, 96–111, Springer. doi:10.1007/978-3-030-17227-5_8

Bapp, F. K.; Dörr, T.; Sandmann, T.; Schade, F.; Becker, J.

2018. SAE International. doi:10.4271/2018-01-1072