Safe and Robust Machine Learning - Hardware Perspective

- Forschungsthema:Safe and Robust Machine Learning, Hardware Architectures, DNN Accelerators

- Typ:Bachelor-/ Masterarbeit

- Betreuung:

Safe and Robust Machine Learning - Hardware Perspective

Kontext

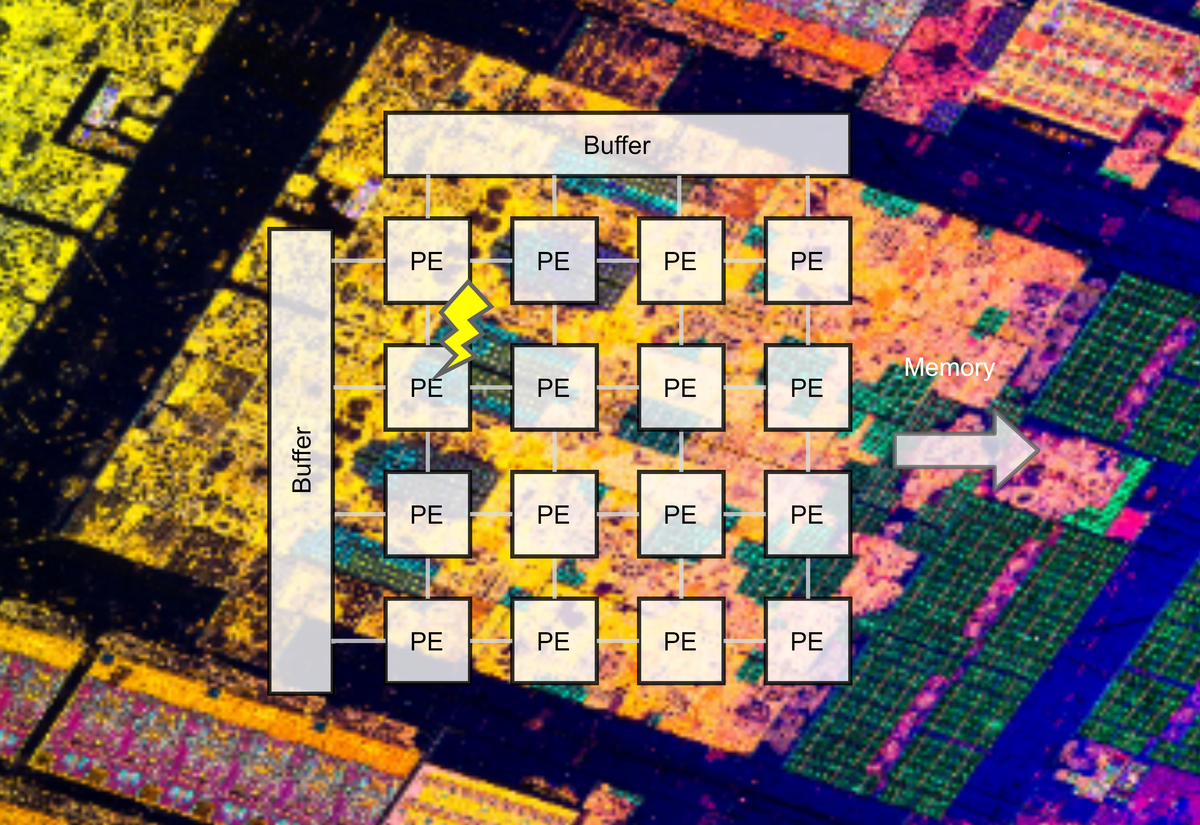

Maschinelles Lernen ist ein vielversprechender Ansatz für die Objekterkennung oder -segmentierung in diversen Bereichen. Mit dem zunehmenden Einsatz von Machine-Learning-Modellen in sicherheitskritischen Anwendungen ist es jedoch auch wichtig, sowohl die Sicherheit/Zuverlässigkeit zu gewährleisten, als auch die Robustheit der ML-Modelle zu erhöhen. Wichtige Aspekte spielen hierbei von Hardwareseite die Absicherung gegen transiente zufällige Fehler. Von Softwareseite ist insbesondere die eine Schätzung der Unsicherheit der neuronalen Netze interessant.

Das Ziel dieser Bachelor-/ Masterarbeit ist es, die Robustheit und Zuverlässigkeit auf Hardwareebene zu verbessern. Dabei können sowohl eigene Hardwarebeschleuniger konzipiert, aber auch vorhandene open-source Hardwarebeschleuniger aus der Forschung analysiert und erweitert werden. Hierbei spielen vor allem RISC-V Plattformen wie Chipyard eine zentrale Rolle.

Aufgaben

- Überblick über die aktuelle Literatur und den Stand der Technik

- Entwurf und Implementierung von Konzepten für Safety-Mechanismen auf Hardwareebene, speziell für DNN Beschleuniger und SoCs

- Evaluation der entwickelten Techniken anhand von Benchmarks und Use-Cases

- Diskussion der Ergebnisse und Ableitung von Schlussfolgerungen

Voraussetzungen

- Große Motivation für das Thema Hardware Design und Machine Learning und selbstständige Problemlösungskompetenz

- Kenntnisse in Hardwareentwicklung sollten vorhanden sein, die konkrete HDL spielt eine untergeordnete Rolle (VHDL, Verilog, Chisel, …)

- Grundlegende Kenntnisse in ML und neuronalen Netzen von Vorteil