DEEP – Data Efficiency in Embedded Processors

- Ansprechperson:

Prof. Dr. Torben Ferber (Verbundkoordinator)

- Projektgruppe:

Prof. Becker

- Förderung:

Bundesministerium für Bildung und Forschung (BMBF), Aktionsplan ErUM-Data, Bekanntmachung vom 11.10.2024 – Software und Algorithmen mit Schwerpunkt auf Künstlicher Intelligenz und Maschinellem Lernen

- Projektbeteiligte:

Karlsruher Institut für Technologie (KIT/ETP, KIT/ITIV), Rheinische Friedrich-Wilhelms-Universität Bonn, Albert-Ludwigs-Universität Freiburg, Technische Universität Hamburg, SiMa Technologies Germany GmbH. Assoziierte Partner: SICK AG, DESY (MSK)

- Starttermin:

01.10.2025

- Endtermin:

30.09.2028

Empowering Data Efficiency In Embedded Processors with Artificial Intelligence (DEEP)

Motivation

Unsere großen Forschungsinfrastrukturen erzeugen riesige und ständig wachsende Datenmengen. Zum Beispiel wird mit dem Übergang zum High-Luminosity Large Hadron Collider (HL-LHC) am CERN die Datenmenge verzehnfacht, was mit vorhandener Technologie nicht bewältigt werden kann und auf nachhaltige Weise nicht möglich ist. Diese Datenflut ist ein gesellschaftliches Problem unserer Informationsgesellschaft. Während moderne Methoden des maschinellen Lernens (ML) in den letzten Jahren zu großen Fortschritten in der Grundlagenforschung geführt haben, betrifft dies bisher hauptsächlich die Analyse zuvor gespeicherter Daten auf konventionellen Rechnerarchitekturen (CPUs, GPUs). Durch die Integration von ML-Algorithmen in eingebettete Prozessoren nahe den Sensoren lässt sich der Bedarf an Datenübertragung und -speicherung bereits an der Quelle erheblich verringern. Die Programmierung solcher Systeme, insbesondere von FPGAs und heterogenen Systems-on-Chip (SoCs), erfordert jedoch spezielles Wissen, das oft über die typische Ausbildungszeit von Promovierenden hinausgeht – eine Hürde für viele Forschungsprojekte.

Projektziele

DEEP (Data Efficiency in Embedded Processors) adressiert als virtuelles nationales Kompetenzzentrum für heterogene SoCs in ErUM die Herausforderungen der Digitalisierung in der Forschung an Universum und Materie. Die Hauptziele sind:

- Entwicklung von Software-Werkzeugen und eines HLS-Frameworks zur Implementierung von ML-Algorithmen auf heterogenen SoCs (AMD Versal, SiMa.ai)

- Aufbau weltführender Expertise für die nächste Generation heterogener SoCs in Deutschland

- Einsatz ultraschneller ML-Methoden an ErUM-Forschungsinfrastrukturen für Beschleunigerkontrolle, Hardware-Trigger und Kalibrierung

- Reduzierung der Anbieterabhängigkeit durch Untersuchung mehrerer SoC-Plattformen

- Wissens- und Technologietransfer in die ErUM-Community und Industrie durch Open-Source-Tools, Workshops und Schulungen

Durchführung

Das Projekt ist in drei Arbeitspakete (WP) gegliedert:

- WP1 – Kooperation: Bündelung, Weiterentwicklung und Verbreitung gemeinsamen Know-hows. Organisation des Konsortiums, interne Qualifizierung, nationale und internationale Zusammenarbeit (DRD7, FastML) sowie Community-Training durch Workshops in Zusammenarbeit mit dem ErUM-Data Hub.

- WP2 – Software und Tools: Erleichterung der ML-Implementierung auf heterogenen SoCs. Algorithmenoptimierung, Entwicklung von Toolchains für AMD Versal FPGAs und AI-Engines basierend auf MLIR und HLS, übergreifende Methodik zur Workload-Partitionierung auf heterogenen Architekturen, sowie Anpassung der SiMa.ai-Toolchain für Echtzeit-Anwendungen.

- WP3 – Algorithmen und Anwendung: Entwicklung und Implementierung von ML-Algorithmen an ErUM-Forschungsinfrastrukturen. Pilotanwendungen umfassen: Echtzeit-GNN-basierte Spurrekonstruktion bei Belle II und AMBER, Alignment-Algorithmen auf heterogenen Architekturen für LHCb, Raum-Zeit-Clustering für Neutronendetektoren (ESS/FRM II), Anomalieklassifikation für European-XFEL-Kavitäten, Echtzeit-Maschinenemulator für PETRA III/IV sowie Technologietransfer zu Industriepartnern.

- Beteiligte Großgeräte: Belle II@SuperKEKB (KEK), LHCb@LHC und AMBER@SPS (CERN), PETRA III/IV und European XFEL (DESY), Heinz Maier-Leibnitz (FRM II) und ESS.

ITIV-Beteiligung

Die Forschungsgruppe von Prof. Becker am Institut für Technik der Informationsverarbeitung (ITIV) bringt umfangreiche Erfahrung in Entwurf und Anwendung rekonfigurierbarer Hardware ein. Die Schwerpunkte umfassen Architekturentwurf für eingebettete Systeme, Hardware/Software-Co-Design und anwendungsspezifische Architekturen. Das ITIV ist an mehreren zentralen Aufgaben beteiligt:

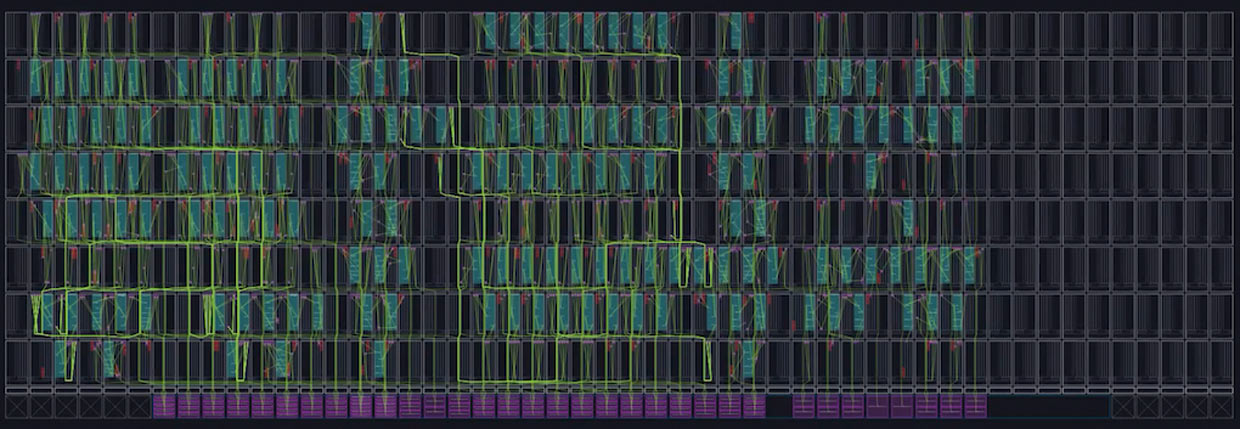

- WP2.T2: Entwicklung der Toolchain für AMD Versal FPGAs, einschließlich HLS-Kernel-Bibliothek und neuartigem Floor-Planning-Konzept

- WP2.T3: Toolchain für AMD Versal AI-Engines, insbesondere Partitionierung von ML-Modellen auf die AI-Engine-Array-Architektur

- WP2.T4: Übergreifende Methodik und Partitionierung – Zusammenführung der FPGA- und AI-Engine-Toolchains zu einem gemeinsamen Workflow mit automatisierter Workload-Verteilung

- WP3.T1: Implementierung der Echtzeit-Spurrekonstruktion mittels Graph Neural Networks bei Belle II auf AMD Versal

- WP3.T7: Transfer der entwickelten ML-Deployment-Lösungen in Industrieanwendungen

Die Gruppe arbeitet bereits mit Prof. Ferbers Gruppe an der Skalierbarkeit dynamischer Graph Neural Networks auf AMD Versal zusammen und betreut gemeinsam MSc- und PhD-Studierende.