Konzept und Entwicklung von High-Performance Hardware Beschleunigern für Neuronale Netze

- Typ:Bachelor-/ Masterarbeit

- Betreuung:

Konzept und Entwicklung von High-Performance Hardware Beschleunigern für Neuronale Netze

Umfeld

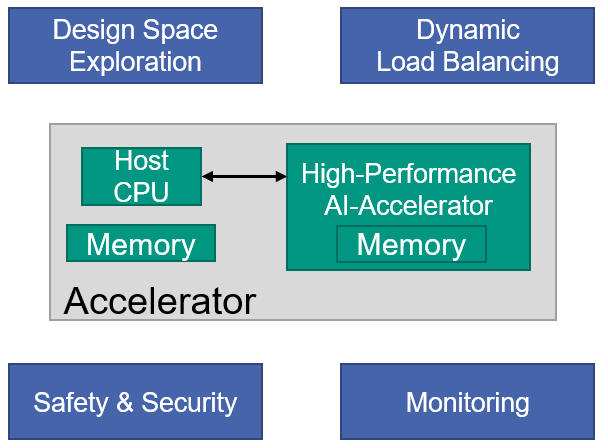

KI-Anwendungen gewinnen für den Automotive Bereich zunehmend an Bedeutung. Um eine effiziente Ausführung dieser Netze zu ermöglichen, sind spezielle Beschleuniger notwendig. Ein Beispiel dafür ist der Gemmini Beschleuniger, ein Open-Source Projekt, das Teil der RISC-V Welt ist.

Er ist vor allem aufgrund seiner hohen Flexibilität interessant. Durch Parametrierung kann die Architektur für unterschiedliche Performanceanforderungen skaliert werden und nicht genutzte Komponenten können entfernt werden.

Aufgabe

Die Aufgabe besteht darin, die grundlegende Architektur weiter zu verbessern, z. B durch Einfügen von Mechanismen, die die Sicherheit der Ausführung garantieren, Sparsity, neue Activation Functions etc. Bei Interesse kann das Thema nach Rücksprache mit den Betreuern frei gewählt werden.

Die Aufgabe kann in die folgenden Schritte geteilt werden:

- Einarbeiten in die grundlegende Architektur

- Einarbeiten in das gewählte Thema

- Konzeption der Hardware Realisierung

- Implementierung, Test und Validierung auf einem FPGA Board

Voraussetzungen

- Kenntnisse in Scala und Chisel sind hilfreich, aber nicht notwendig

- Interesse an Beschleuniger- und Hardware-Design

- Kenntnisse über den Einsatz von KI-Algorithmen auf Beschleunigern