Laufzeitadaptive Many-Core-Architekturen

Moderne Prozessoren müssen immer mehr gegensätzlich Anforderungen erfüllen. Prozessoren sollen nicht nur immer leistungsfähiger und effizienter, sondern auch immer fehlerresistenter werden. Eine Lösung, um diese widersprüchlichen Anforderungen zu erfüllen, sind adaptive Prozessorarchitekturen, welche sich den Anforderungen und der Situation anpassen. Durch eine Adaptivität zur Laufzeit kann während des Betriebes der beste Kompromiss zwischen den Anforderungen zu erzielen.

Fehlertoleranzmechanismen auf Basis adaptiver Hardwareredundanz

Mit der zunehmenden Automatisierung des Fahrens steigt das Risiko, dass elektronische Fehlfunktionen im Fahrzeug zu physischen Schäden führen. Daher müssen in diesem Zusammenhang relevante Komponenten immer häufiger so ausgelegt werden, dass sie trotz solcher Fehlfunktionen ein definiertes Mindestmaß an Funktionalität zuverlässig erbringen. Hierfür ist der Einsatz geeigneter Fehlertoleranzmechanismen notwendig. Wir forschen daran, solche Mechanismen unter Verwendung adaptiver Hardwareredundanz besonders kosteneffizient zu realisieren.

Absicherung von KI-Beschleunigern im sicherheitskritischen Umfeld

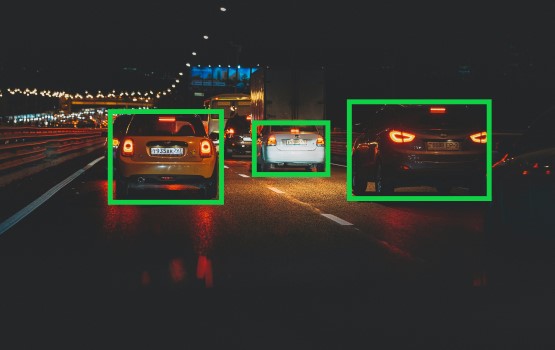

Die Grundlage für autonomes Fahren und weitere sicherheitskritische Anwendungen ist die zuverlässige Erkennung der unmittelbaren Umgebung mithilfe von Kameras, sowie Radar- und Lidarsensoren. Die besten Ergebnisse zur Objekterkennung liefert hier maschinelles Lernen, z.B. Convolutional Neural Networks. Die Herausforderung besteht akut darin, diese neuronalen Netze in eingebettete Systeme zu integrieren und dabei die Zuverlässigkeit sicherzustellen. Insbesondere zufällige Hardwarefehler sowie die Unfähigkeit, die eigene Unsicherheit zu schätzen, verhindern noch den sicherheitskritischen Einsatz.

Betreute studentische Arbeiten (Auswahl)

-

SA: “Fault Tolerance in Embedded Mixed Critical Systems”

-

BA: “Concept and implementation of a dynamic lockstep architecture for a LEON3 Many-Core System”

-

BA: “Concept and implementation of a cache-based fault-tolerant mechanism for the LEON3 processor”

-

MA: “Concept and Implementation of an adaptive cache architecture for a LEON3 Many-Core System”

-

MA: “Investigation of machine learning approaches for error detection in control flow based on bus snooping”

Publikationen

Hoefer, J.; Gauß, M.; Adams, M.; Kreß, F.; Kempf, F.; Karle, C.; Harbaum, T.; Barth, A.; Becker, J.

2024. 2024 IEEE International Symposium on Circuits and Systems (ISCAS), Singapore, Singapore, 19-22 May 2024, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/ISCAS58744.2024.10557955

Kempf, F.; Hoefer, J.; Harbaum, T.; Becker, J.; Fasfous, N.; Frickenstein, A.; Voegel, H.-J.; Friedrich, S.; Wittig, R.; Matúš, E.; Fettweis, G.; Lueders, M.; Blume, H.; Benndorf, J.; Grantz, D.; Zeller, M.; Engelke, D.; Eickel, K.-H.

2023. 2023 Design, Automation & Test in Europe Conference & Exhibition (DATE), Antwerp, Belgium, 17-19 April 2023, Institute of Electrical and Electronics Engineers (IEEE). doi:10.23919/DATE56975.2023.10137257

Kempf, F.; Höfer, J.; Hotfilter, T.; Becker, J.

2023. 2023 IEEE 16th International Symposium on Embedded Multicore/Many-core Systems-on-Chip (MCSoC), 276 – 283, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/MCSoC60832.2023.00048

Hotfilter, T.; Hoefer, J.; Merz, P.; Kreß, F.; Kempf, F.; Harbaum, T.; Becker, J.

2023. 2023 IEEE 36th International System-on-Chip Conference (SOCC), Santa Clara, USA, 05-08 September 2023, 1–6, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC58585.2023.10256738

Kreß, F.; Pfau, J.; Kempf, F.; Schmidt, P.; He, Z.; Harbaum, T.; Becker, J.

2023. 2023 IEEE Nordic Circuits and Systems Conference (NorCAS), 31st October - 1st November 2023, Aalborg, Denmark, 1–7, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/NorCAS58970.2023.10305469

Hotfilter, T.; Höfer, J.; Kreß, F.; Kempf, F.; Kraft, L.; Harbaum, T.; Becker, J.

2023. 2023 IEEE 5th International Conference on Artificial Intelligence Circuits and Systems (AICAS), 1–5, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/AICAS57966.2023.10168566

Kempf, F.; Becker, J.

2023. 2023 12th Mediterranean Conference on Embedded Computing (MECO), 1–5, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/MECO58584.2023.10154986

Hoefer, J.; Kempf, F.; Hotfilter, T.; Kreß, F.; Harbaum, T.; Becker, J.

2023. Proceedings of the Great Lakes Symposium on VLSI 2023, 287–292, Association for Computing Machinery (ACM). doi:10.1145/3583781.3590226

Kempf, F.; Kühbacher, C.; Mellwig, C.; Altmeyer, S.; Ungerer, T.; Becker, J.

2023. 2022 25th Euromicro Conference on Digital System Design (DSD), 704–711, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/DSD57027.2022.00099

Kempf, F.; Höfer, J.; Kreß, F.; Hotfilter, T.; Harbaum, T.; Becker, J.

2022. Conference Proceedings: 2022 IEEE 35th International System-on-Chip Conference (SOCC) Ed.: S. Sezer, 1–6, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC56010.2022.9908110

Hotfilter, T.; Kreß, F.; Kempf, F.; Becker, J.; Baili, I.

2022. 2022 IEEE Computer Society Annual Symposium on VLSI (ISVLSI), Nicosia, Cyprus, 04-06 July 2022, 371–372. doi:10.1109/ISVLSI54635.2022.00082

Hotfilter, T.; Kreß, F.; Kempf, F.; Becker, J.; Haro, J. M. De; Jiménez-González, D.; Moretó, M.; Álvarez, C.; Labarta, J.; Baili, I.

2022. 2022 Design, Automation & Test in Europe Conference & Exhibition (DATE), Antwerp, Belgium, 14-23 March 2022, 628–631, Institute of Electrical and Electronics Engineers (IEEE). doi:10.23919/DATE54114.2022.9774716

Hotfilter, T.; Hoefer, J.; Kreß, F.; Kempf, F.; Becker, J.

2021. IEEE 34th International System-on-Chip Conference (SOCC), 14th-17th September 2021, Las Vegas, Nevada, USA, 83–88, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC52499.2021.9739212

Kempf, F.; Hartmann, T.; Bähr, S.; Becker, J.

2021. 2021 IEEE Computer Society Annual Symposium on VLSI (ISVLSI): 7-9 July 2021, Tampa, FL, USA, 7–12, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/ISVLSI51109.2021.00013

Hotfilter, T.; Kempf, F.; Becker, J.; Reinhardt, D.; Baili, I.

2020. 6th IEEE World Forum on Internet of Things, WF-IoT 2020, New Orleans, United States, 2 - 16 June 2020, Art.Nr. 9221396, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/WF-IoT48130.2020.9221396

Reder, S.; Kempf, F.; Bucher, H.; Becker, J.; Alefragis, P.; Voros, N.; Skalistis, S.; Derrien, S.; Puaut, I.; Oey, O.; Stripf, T.; Ferdinand, C.; David, C.; Ulbig, P.; Mueller, D.; Durak, U.

2019. Journal of aerospace information systems, 16 (11), 521–533. doi:10.2514/1.I010749

Kempf, F.; Anantharajaiah, N.; Masing, L.; Becker, J.

2019. 32nd IEEE International System on Chip Conference, SOCC 2019; Singapore; Singapore; 3 September 2019 through 6 September 2019. Ed.: D. Zhao, 39–44, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC46988.2019.1570558594

Anantharajaiah, N.; Kempf, F.; Masing, L.; Lesniak, F. M.; Becker, J.

2019. Proceedings of the 12th International Workshop on Network on Chip Architectures (NoCArc 2019), Columbus, OH, Ocober 12-13, 2019, 1–6, Association for Computing Machinery (ACM). doi:10.1145/3356045.3360718

Baehr, S.; Kempf, F.; Becker, J.

2018. Proceedings of the 18th International Conference on Nanotechnology (IEEE-NANO 2018), Cork, IRL, July 23-26, 2018, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/NANO.2018.8626239

Baehr, S.; Kempf, F.; Becker, J.

2018. Proceedings of the 31th IEEE International System-on-Chip Conference (SOCC), Arlington, VA, September 4-7, 2018, 174–179, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC.2018.8618563