Overview

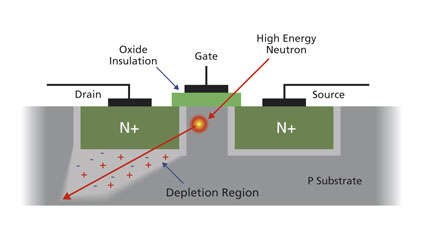

Embedded electronic systems are subject to a variety of different requirements. Above all, the demand for computing power has steadily increased for decades. To cover this, the use of modern processors in Multi-Core and networked architectures is unavoidable. Increases in complexity however make such architectures more susceptible to random failures, causing potentially catastrophic effects. Radiation can randomly affect transistor cells (Fig. 1), causing the running application to behave unpredictably and unreliably.

Fig. 1 High energy neutron effects on an N-MOS transistor.

Safety-critical environments in domains such as avionics, aerospace and automated driving pose a massive challenge to the evolution of computational power: despite the complexity of using such advanced technologies, the system must still meet existing reliability and availability requirements.

Fig. 2 Effected of Soft-Errors on a processor pipeline

Soft-Errors are a type of error in a computer system that affect signals or data in an information system, they can occur in communication or storage units, such as buses or memories, including the internal general purpose registers of a CPU (Fig. 2). When a soft-error modifies a working data, this may cause a Data Corruption Error, generating an application response or output that is incorrect. If this value is part of a control structure such as if-else statements or loop structures, the program may behave unexpectedly. These type of errors are Control Flow Error (CFE).

The use of multi-core processors in an efficient manner in a safety-critical environment is the subject of this research.

Tasks Description

The main objective of this work is the development of a hardware trace-decoder unit for the implementation of a CFE monitor. This subsystem should be able to read and analyse the program trace flow of each core in a 4 core CPU unit. Decoding the trace in real-time is the first step in for the implementation of a Control Flow Error Detection unit. With static software analysis, we can generate a graph that contains all possible decision points (jumps and branches) of the program before having to execute it in the platform. This graph is the program’s Control Flow Graph (CFG). By comparing the output of the decoded trace with the CFG, we can identify any control flow errors or synchronization errors among cores. Once it identifies an error, the monitor can notify a management unit or supervisor system and the appropriate action based on the type and criticality of application can be taken.

Requirements

The theoretical part of this thesis requires knowledge of embedded electronic systems. Previous knowledge of system reliability is helpful but not required. For the practical part, good programming skills are required. A detailed list of skills follows:

- Experience in VHDL programming and development is required.

- Experience with Leon3 / GRLIB is helpful.

- Knowledge of embedded C and/or Assembler programming is helpful.

- Knowledge in embedded CPU architectures is helpful.