Projekt ARGO

![]()

Project Goals

The goal of the ARGO (WCET-Aware Parallelization of Model-Based Applications for Heterogeneous Parallel Systems) research project is to develop a tool-chain which translates a model-based Scilab/Xcos application into multi-core optimized C code with guaranteed real-time constraints. This shall be achieved by developing WCET aware automatic parallelization algorithms and a WCET analysis tool for heterogeneous multi-core architectures and parallel programs. Furthermore ARGO aims to provide a cross-layer programming interface, which allows end users to interactively control the automated parallelization process if needed.

Project Key Facts

Funding agency: EU Horizon 2020 Research and Innovation Programme

Budget: 3.9 Millionen Euro

Coordinator: Jürgen Becker

Start date: 1.1.2016

End date: 31.12.2018

Official web site: https://www.argo-project.eu/

E-Mail contact: mail∂argo-project.eu

Project Partners

The ARGO project brings together 8 partners from industry and academia in order to address the most relevant aspects of the complex subject of automatic parallelization of model-based applications for time-predictable, heterogeneous parallel systems.

The project is funded by the EU Horizon 2020 Research and Innovation Programme.

The ARGO Approach

Increasing performance and reducing cost, while maintaining safety levels and programmability are the key demands for embedded and cyber-physical systems in European domains, e.g. aerospace, automation, and automotive. For many applications, the necessary performance with low energy consumption can only be provided by customized computing platforms based on heterogeneous many-core architectures. However, their parallel programming with time-critical embedded applications suffers from a complex toolchain and programming process.

The ARGO research project will address this challenge with a holistic approach for programming heterogeneous multi- and many-core architectures using automatic parallelization of model-based real-time applications. ARGO will enhance WCET-aware automatic parallelization by a cross-layer programming approach combining automatic tool-based and user-guided parallelization to reduce the need for expertise in programming parallel heterogeneous architectures. The ARGO approach will be assessed and demonstrated by prototyping comprehensive time-critical applications from both aerospace and industrial automation domains on customized heterogeneous many-core platforms.

The challenging research and innovation action will be achieved by the unique ARGO consortium that brings together industry, leading research institutes and universities. High class SMEs such as Recore Systems, Scilab Enterprises and AbsInt will contribute their diverse know-how in heterogeneous many-core technologies, model-based design environments and WCET calculation. The academic partners will contribute their outstanding expertise in code transformations, automatic parallelization and system-level WCET analysis.

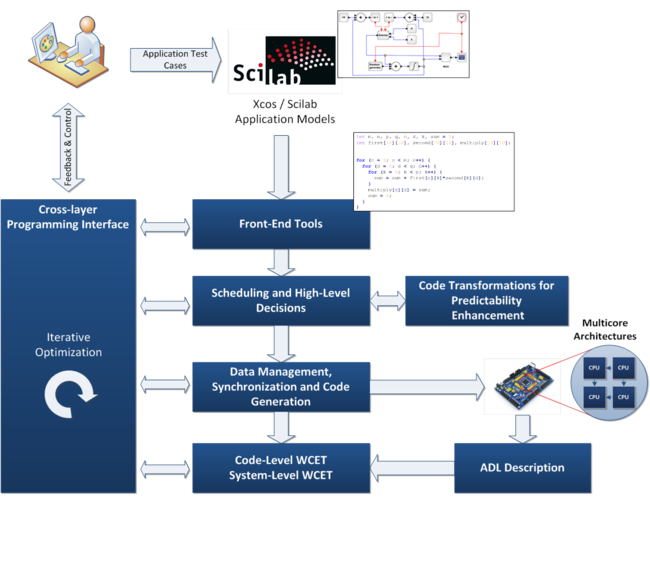

ARGO Tool-Flow

The ARGO tool-chain will translate model-based Scilab/Xcos applications into multi-core optimized C code with guaranteed real-time constraints. This shall be achieved by developing WCET aware automatic parallelization algorithms and a WCET analysis tool for heterogeneous multi-core architectures and parallel programs. Furthermore ARGO aims to provide a cross-layer programming interface, which allows end users to interactively control the automated parallelization process if needed.

The following figure shows an overview of the planned tool-flow:

ITIV Contribution

The ITIV coordinates the ARGO project and contributes with technical expertise in the areas of Automatic Parallel Code Generation, Multi-Core Target Architectures, the Scilab/Xcos Front-End tools as well as the ARGO Cross-Layer Programming Interface.

In detail, ITIV researchers will bring the following know-how into the recently launched ARGO project:

• Through its participation in the EU FP7-ICT project ALMA (https://alma-project.eu/), ITIV researchers have acquired significant knowledge and expertise on compiler research, parallel code generation and cycle-approximate simulation of multiprocessor systems. This includes transforming Scilab source code to statically analysable C code that serves as the input for the parallelizing toolchain developed in ALMA. To this toolchain, they contributed algorithms for mapping variables to memory locations to minimize access latencies and algorithms for placing communication between tasks executed on different processors in order to minimize wait times and improve the performance achieved by the parallelization.

• Through its participation in the DFG Transregional Collaborative Research Center 89 “Invasive Computing” (InvasIC, https://www.invasic.de), ITIV researchers have acquired significant knowledge and expertise in heterogeneous many-core architectures, scalable networks-on-chips that enable WCET-analyzable communication between components of large-scale processing systems, and FPGA prototyping of these systems.

March 2, 2017: Technical Meeting in Braunschweig, Germany. The ARGO team in front of the flight simulator AVES.

Publications

WCET-Aware Parallelization of Model-Based Applications for Heterogeneous Parallel System, 11th HiPEAC Conference in Prague, January 2016