Background

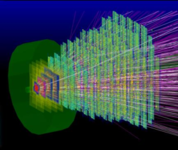

The Compressed Baryonic Matter (CBM) experiment will be one of the major scientific pillars of the future Facility for Antiproton and Ion Research (FAIR) in Darmstadt. The experiment aims to expanding our knowledge about the matter itself, which requires very fast detectors and a novel data read-out and analysis concept.

One of the most important electronic subsystems in the experiment is the Timing and Fast Control (TFC) subsystem that is being developed at ITIV. Its task is to make front-end electronics and data processing nodes operate synchronously, so that the data stream is consistent and organised. It has a tree-like master-slave structure and is being developed using HW-SW co-design approach.

You will learn

Principles of synchronisation in a scalable real-time data acquisition and processing system with long-term stability.

Tasks and responsibilities

- Analysis and optimisation of the clock distribution scheme

- Exploration of new technical solutions for node synchronisation

- Development of new functionality for integration into the experimental setup

Requirements

- C programming skills

- HDL design skills

- Fluent English