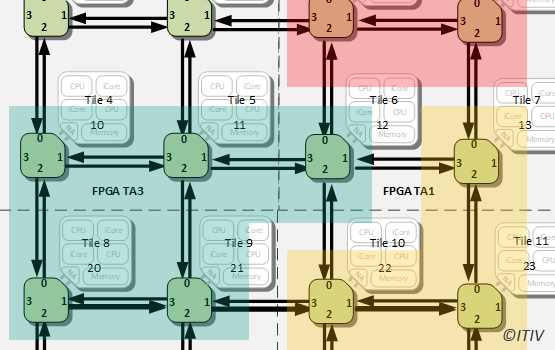

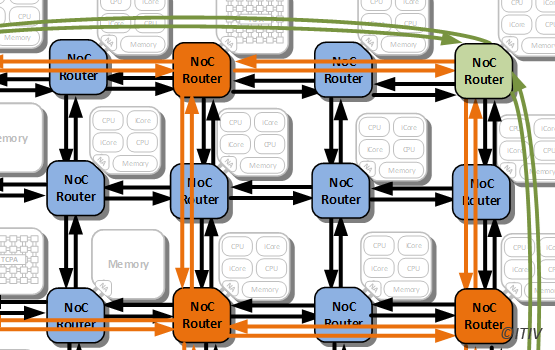

Adaptive Networks-on-Chip für Mixed-Criticality Systeme

Um den Ressourcenverbrauch zu reduzieren, werden zunehmend mehrere Anwendungen mit unterschiedlicher Kritikalität auf derselben System-on-Chip-Plattform (SoC) ausgeführt. Diese Plattformen bewegen sich in Richtung Multi/Many-Core-Architekturen und können Networks-on-Chip (NoC) für die Kommunikation nutzen. Mit der zunehmenden Anzahl von Kernen auf solchen Plattformen nimmt die Komplexität der Verbindungen zu und wird zu einem begrenzenden Faktor für die Leistung. Die Leistung solcher Systeme kann verbessert werden, wenn das NoC in der Lage ist, sich zur Laufzeit an die Anforderungen der verschiedenen Anwendungen anzupassen.

Routing-Algorithmen für non-mesh based Topologien in einem Networks-on-Chip

Die Mesh-Topologie wird häufig in Networks-on-Chip (NoC) implementiert, da sie skalierbar, einfach zu implementieren und einheitlich ist. Mit der zunehmenden Komplexität von On-Chip-Verbindungen für große Multi-/Many-Core-Systeme kann die Verwendung der Mesh-Topologie aufgrund der hohen Anzahl von Sprüngen ineffizient werden. Hierarchische und mehrschichtige Topologien sowie unregelmäßige Topologien werden untersucht, um die Gesamtleistung des Systems zu verbessern. Das Routing in solchen NoCs kann zu einer Herausforderung werden, weshalb hier Untersuchungen zu Routing-Algorithmen für reguläre und unregelmäßige Topologien durchgeführt werden.

Lehre

Übungen zu 2311616 Communication Systems and Protocols

Seminar: Eingebettete Systeme (https://www.itiv.kit.edu/english/60_6321.php)

Betreute abgeschlossene studentische Arbeiten (Auswahl)

Seminar: Eingebettete Systeme:

- Seminar: "Introduction and Analysis of Methods for Adaptive Networks-on-Chip"

- Seminar: "Quality of Service in Adaptive Networks-on-Chip"

Bachelor / Master thesis:

- MA: "Design and Implementation of an ACO Based Router for Mixed Criticality NoCs"

- MA: "Improving Quality of Service in Adaptive Networks-on-Chip for Mixed-Criticality System"

- MA. “Performance Comparison between the SXP and PCI Express Protocol with a Refinement Approach of SXP with Security”

- BA: "Design and Implementation of a Self-Adaptive NoC"

Publikationen

Anantharajaiah, N.; Lesniak, F.; Harbaum, T.; Becker, J.

2023. 2023 IEEE 16th International Symposium on Embedded Multicore/Many-core Systems-on-Chip (MCSoC), 38 – 44, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/MCSoC60832.2023.00014

Anantharajaiah, N.; Xu, Y.; Lesniak, F.; Harbaum, T.; Becker, J.

2023. IEEE Computer Society Annual Symposium on VLSI (ISVLSI), 1–6, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/ISVLSI59464.2023.10238569

Chu, A.; Hermann, C. M.; Silz, J.; Pfau, J.; Barón, K. M.; Anantharajaiah, N.; Schmidt, P.; Hotfilter, T.; Xie, X.; Becker, J.; Kallfass, I.; Roth-Stielow, J.; Stork, W.

2023. IEEE EUROCON 2023 - 20th International Conference on Smart Technologies, 665–670, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/EUROCON56442.2023.10199076

Lesniak, F.; Anantharajaiah, N.; Harbaum, T.; Becker, J.

2023. RAPIDO ’23: Proceedings of the DroneSE and RAPIDO: System Engineering for constrained embedded systems, 31–38, Association for Computing Machinery (ACM). doi:10.1145/3579170.3579262

Anantharajaiah, N.; Becker, J.

2023. 2022 25th Euromicro Conference on Digital System Design (DSD), 174–180, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/DSD57027.2022.00032

de Barros, J. B.; Anantharajaiah, N.; Ayala-Rincón, M.; Llanos, C. H.; Becker, J.

2022. Microprocessors and Microsystems, 94, Art.-Nr.: 104668. doi:10.1016/j.micpro.2022.104668

Anantharajaiah, N.; Knopf, F.; Becker, J.

2021. Proceedings 34th IEEE International System-on-Chip Conference (SOCC): September 14–17, 2021, Virtual. Ed.: G. Qu, 248–253, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC52499.2021.9739596

Anantharajaiah, N.; Zhang, Z.; Becker, J.

2021. Applied Reconfigurable Computing. Ed.: S. Derrien, 125–139, Springer Nature Switzerland. doi:10.1007/978-3-030-79025-7_9

Barros, J. B. de; Anantharajaiah, N.; Ayala-Rincon, M.; Llanos, C. H.; Becker, J.

2020. 2020 IEEE Nordic Circuits and Systems Conference (NorCAS), 1–7, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/NorCAS51424.2020.9265134

Kempf, F.; Anantharajaiah, N.; Masing, L.; Becker, J.

2019. 32nd IEEE International System on Chip Conference, SOCC 2019; Singapore; Singapore; 3 September 2019 through 6 September 2019. Ed.: D. Zhao, 39–44, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/SOCC46988.2019.1570558594

Anantharajaiah, N.; Kempf, F.; Masing, L.; Lesniak, F. M.; Becker, J.

2019. Proceedings of the 12th International Workshop on Network on Chip Architectures (NoCArc 2019), Columbus, OH, Ocober 12-13, 2019, 1–6, Association for Computing Machinery (ACM). doi:10.1145/3356045.3360718

Masing, L.; Srivatsa, A.; Kreß, F.; Anantharajaiah, N.; Herkersdorf, A.; Becker, J.

2018. IEEE 12th International Symposium on Embedded Multicore/Many-core Systems-on-Chip (MCSoC), Hanoi, VN, September 12-14, 2018, 138–145, Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/MCSoC2018.2018.00033

Masing, L.; Srivatsa, A.; Kreß, F.; Anantharajaiah, N.; Herkersdorf, A.; Becker, J.

2018. 12th International Symposium on Embedded Multicore/Many-core Systems-on-Chip (MCSoC 2018), Hanoi, Vietnam, 12.–14. September 2018